Attrezzatura per l'assottigliamento dei wafer per la lavorazione di wafer in zaffiro/SiC/Si da 4 a 12 pollici

Principio di funzionamento

Il processo di assottigliamento dei wafer avviene in tre fasi:

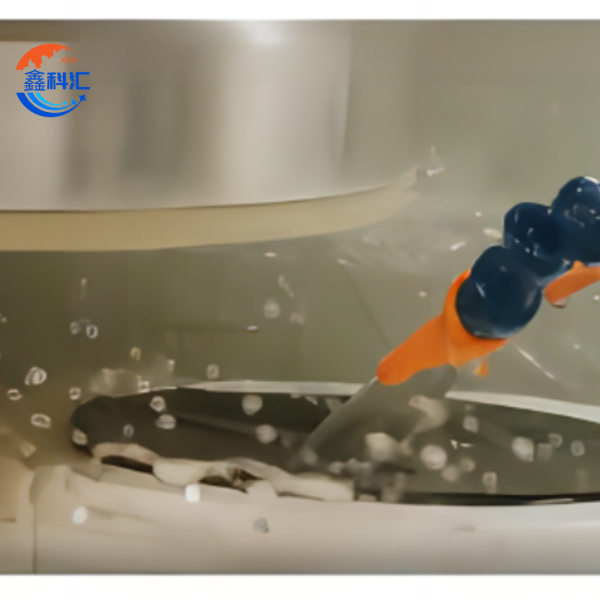

Rettifica grezza: una mola diamantata (granulometria 200–500 μm) rimuove 50–150 μm di materiale a 3000–5000 giri/min per ridurre rapidamente lo spessore.

Rettifica fine: una mola più fine (granulometria 1–50 μm) riduce lo spessore a 20–50 μm a <1 μm/s per ridurre al minimo i danni al sottosuolo.

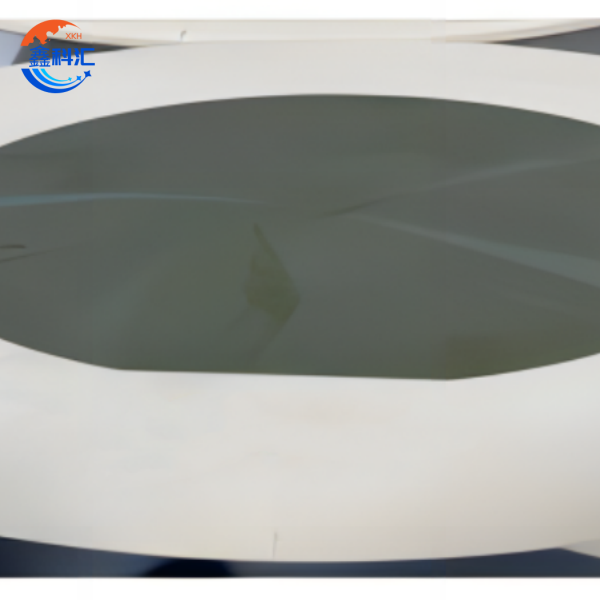

Lucidatura (CMP): una sospensione chimico-meccanica elimina i danni residui, ottenendo Ra <0,1 nm.

Materiali compatibili

Silicio (Si): standard per wafer CMOS, assottigliato a 25 μm per l'impilamento 3D.

Carburo di silicio (SiC): richiede mole diamantate specializzate (concentrazione di diamante all'80%) per la stabilità termica.

Zaffiro (Al₂O₃): diluito a 50 μm per applicazioni LED UV.

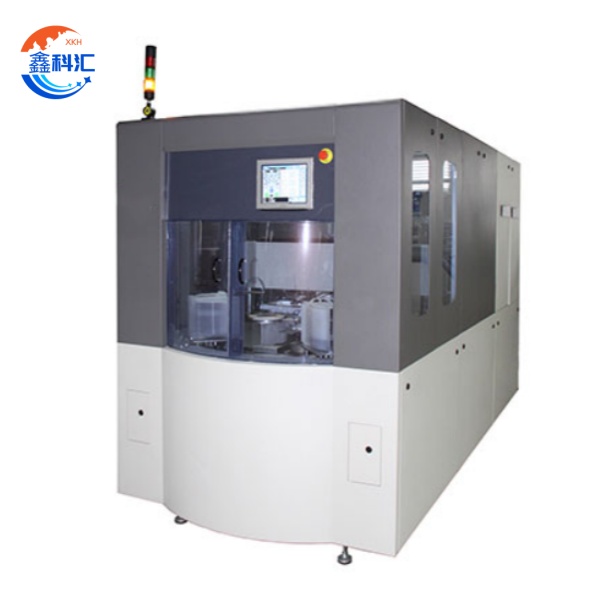

Componenti del sistema principale

1. Sistema di macinazione

Rettificatrice a doppio asse: combina la macinazione grossolana/fine in un'unica piattaforma, riducendo il tempo di ciclo del 40%.

Mandrino aerostatico: gamma di velocità da 0 a 6000 giri/min con eccentricità radiale <0,5 μm.

2. Sistema di movimentazione dei wafer

Mandrino a vuoto: forza di tenuta >50 N con precisione di posizionamento di ±0,1 μm.

Braccio robotico: trasporta wafer da 4 a 12 pollici a 100 mm/s.

3. Sistema di controllo

Interferometria laser: monitoraggio dello spessore in tempo reale (risoluzione 0,01 μm).

Feedforward basato sull'intelligenza artificiale: prevede l'usura delle ruote e regola automaticamente i parametri.

4. Raffreddamento e pulizia

Pulizia a ultrasuoni: rimuove particelle >0,5 μm con un'efficienza del 99,9%.

Acqua deionizzata: raffredda il wafer a <5°C sopra la temperatura ambiente.

Vantaggi principali

1. Precisione ultra elevata: TTV (variazione dello spessore totale) <0,5 μm, WTW (variazione dello spessore all'interno del wafer) <1 μm.

2. Integrazione multiprocesso: combina rettifica, CMP e incisione al plasma in un'unica macchina.

3. Compatibilità dei materiali:

Silicio: riduzione dello spessore da 775 μm a 25 μm.

SiC: raggiunge un TTV <2 μm per applicazioni RF.

Wafer drogati: wafer di InP drogati con fosforo con deriva di resistività <5%.

4. Automazione intelligente: l'integrazione MES riduce l'errore umano del 70%.

5. Efficienza energetica: consumo energetico ridotto del 30% grazie alla frenata rigenerativa.

Applicazioni chiave

1. Imballaggio avanzato

• Circuiti integrati 3D: l'assottigliamento dei wafer consente l'impilamento verticale di chip logici/di memoria (ad esempio, stack HBM), ottenendo una larghezza di banda 10 volte superiore e un consumo energetico ridotto del 50% rispetto alle soluzioni 2.5D. L'apparecchiatura supporta l'ibrid bonding e l'integrazione TSV (Through-Silicon Via), fondamentali per i processori AI/ML che richiedono un passo di interconnessione <10 μm. Ad esempio, i wafer da 12 pollici assottigliati a 25 μm consentono l'impilamento di oltre 8 strati mantenendo una deformazione <1,5%, essenziale per i sistemi LiDAR per autoveicoli.

• Packaging Fan-Out: riducendo lo spessore del wafer a 30 μm, la lunghezza dell'interconnessione si riduce del 50%, riducendo al minimo il ritardo del segnale (<0,2 ps/mm) e consentendo chiplet ultrasottili da 0,4 mm per SoC mobili. Il processo sfrutta algoritmi di rettifica con compensazione dello stress per prevenire la deformazione (controllo TTV >50 μm), garantendo affidabilità nelle applicazioni RF ad alta frequenza.

2. Elettronica di potenza

• Moduli IGBT: l'assottigliamento a 50 μm riduce la resistenza termica a <0,5 °C/W, consentendo ai MOSFET SiC da 1200 V di funzionare a temperature di giunzione di 200 °C. Le nostre apparecchiature utilizzano una rettifica multistadio (grossolana: grana da 46 μm → fine: grana da 4 μm) per eliminare i danni sottosuperficiali, ottenendo oltre 10.000 cicli di affidabilità termica. Questo è fondamentale per gli inverter per veicoli elettrici, dove i wafer SiC da 10 μm di spessore migliorano la velocità di commutazione del 30%.

• Dispositivi di potenza GaN su SiC: l'assottigliamento dei wafer a 80 μm migliora la mobilità degli elettroni (μ > 2000 cm²/V·s) per HEMT GaN da 650 V, riducendo le perdite di conduzione del 18%. Il processo utilizza il dicing assistito da laser per prevenire le crepe durante l'assottigliamento, ottenendo una scheggiatura dei bordi <5 μm per gli amplificatori di potenza RF.

3. Optoelettronica

• LED GaN su SiC: i substrati in zaffiro da 50 μm migliorano l'efficienza di estrazione della luce (LEE) all'85% (rispetto al 65% dei wafer da 150 μm) riducendo al minimo l'intrappolamento dei fotoni. Il controllo TTV ultra-basso delle nostre apparecchiature (<0,3 μm) garantisce un'emissione LED uniforme su wafer da 12 pollici, fondamentale per i display Micro-LED che richiedono un'uniformità di lunghezza d'onda <100 nm.

• Fotonica al silicio: i wafer di silicio da 25 μm di spessore consentono una perdita di propagazione inferiore di 3 dB/cm nelle guide d'onda, essenziale per i transceiver ottici da 1,6 Tbps. Il processo integra la levigatura CMP per ridurre la rugosità superficiale a Ra <0,1 nm, migliorando l'efficienza di accoppiamento del 40%.

4. Sensori MEMS

• Accelerometri: i wafer di silicio da 25 μm raggiungono un SNR >85 dB (rispetto ai 75 dB dei wafer da 50 μm) aumentando la sensibilità allo spostamento della massa di prova. Il nostro sistema di rettifica a doppio asse compensa i gradienti di stress, garantendo una deriva della sensibilità <0,5% tra -40 °C e 125 °C. Le applicazioni includono il rilevamento di incidenti automobilistici e il tracciamento del movimento AR/VR.

• Sensori di pressione: l'assottigliamento a 40 μm consente intervalli di misurazione da 0 a 300 bar con un'isteresi FS <0,1%. Utilizzando un legame temporaneo (supporti in vetro), il processo evita la frattura del wafer durante l'incisione sul retro, ottenendo una tolleranza di sovrapressione <1 μm per i sensori IoT industriali.

• Sinergia tecnica: le nostre apparecchiature per l'assottigliamento dei wafer uniscono la rettifica meccanica, la lucidatura CMP e l'incisione al plasma per affrontare diverse sfide legate ai materiali (Si, SiC, Zaffiro). Ad esempio, il GaN su SiC richiede una rettifica ibrida (mole diamantate + plasma) per bilanciare durezza ed espansione termica, mentre i sensori MEMS richiedono una rugosità superficiale inferiore a 5 nm tramite lucidatura CMP.

• Impatto sul settore: consentendo wafer più sottili e dalle prestazioni più elevate, questa tecnologia stimola innovazioni nei chip AI, nei moduli 5G mmWave e nell'elettronica flessibile, con tolleranze TTV <0,1 μm per i display pieghevoli e <0,5 μm per i sensori LiDAR per autoveicoli.

Servizi XKH

1. Soluzioni personalizzate

Configurazioni scalabili: modelli di camere da 4–12 pollici con carico/scarico automatizzati.

Supporto al doping: ricette personalizzate per cristalli drogati con Er/Yb e wafer InP/GaAs.

2. Supporto end-to-end

Sviluppo del processo: prove gratuite con ottimizzazione.

Formazione globale: workshop tecnici annuali su manutenzione e risoluzione dei problemi.

3. Elaborazione multi-materiale

SiC: assottigliamento del wafer fino a 100 μm con Ra <0,1 nm.

Zaffiro: spessore 50 μm per finestre laser UV (trasmittanza >92% a 200 nm).

4. Servizi a valore aggiunto

Materiali di consumo: mole diamantate (oltre 2000 wafer/durata) e fanghi CMP.

Conclusione

Questa attrezzatura per l'assottigliamento dei wafer offre precisione leader del settore, versatilità multi-materiale e automazione intelligente, rendendola indispensabile per l'integrazione 3D e l'elettronica di potenza. I servizi completi di XKH, dalla personalizzazione alla post-elaborazione, garantiscono ai clienti efficienza dei costi ed eccellenza nelle prestazioni nella produzione di semiconduttori.