Wafer SiC da 4 pollici Substrati SiC semi-isolanti 6H di grado primario, di ricerca e fittizio

Specifiche del prodotto

| Grado | Grado di produzione Zero MPD (grado Z) | Grado di produzione standard (grado P) | Grado fittizio (grado D) | ||||||||

| Diametro | 99,5 mm~100,0 mm | ||||||||||

| 4H-SI | 500 μm±20 μm | 500 μm±25 μm | |||||||||

| Orientamento del wafer |

Fuori asse: 4,0° verso < 1120 > ±0,5° per 4H-N, Sull'asse: <0001>±0,5° per 4H-SI | ||||||||||

| 4H-SI | ≤1cm-2 | ≤5 centimetri-2 | ≤15 centimetri-2 | ||||||||

| 4H-SI | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |||||||||

| Orientamento primario piatto | {10-10} ±5,0° | ||||||||||

| Lunghezza piana primaria | 32,5 mm±2,0 mm | ||||||||||

| Lunghezza piatta secondaria | 18,0 mm±2,0 mm | ||||||||||

| Orientamento secondario piatto | Faccia in silicone verso l'alto: 90° CW. da Prime piatto ±5,0° | ||||||||||

| Esclusione del bordo | 3 millimetri | ||||||||||

| LTV/TTV/Arco/Ordito | ≤3 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||||||||

| Rugosità | Faccia C | Polacco | Ra≤1 nm | ||||||||

| Si faccia | CMP | Ra≤0,2 nm | Ra≤0,5 nm | ||||||||

| Crepe sui bordi causate da luce ad alta intensità | Nessuno | Lunghezza cumulativa ≤ 10 mm, singola lunghezza≤2 mm | |||||||||

| Piastre esagonali ad alta intensità luminosa | Area cumulativa ≤0,05% | Area cumulativa ≤0,1% | |||||||||

| Aree politipiche mediante luce ad alta intensità | Nessuno | Area cumulativa ≤3% | |||||||||

| Inclusioni visive di carbonio | Area cumulativa ≤0,05% | Area cumulativa ≤3% | |||||||||

| Graffi sulla superficie del silicio causati dalla luce ad alta intensità | Nessuno | Lunghezza cumulativa ≤1*diametro del wafer | |||||||||

| Chip di bordo ad alta intensità luminosa | Nessuno consentito ≥0,2 mm di larghezza e profondità | 5 consentiti, ≤1 mm ciascuno | |||||||||

| Contaminazione della superficie del silicio ad alta intensità | Nessuno | ||||||||||

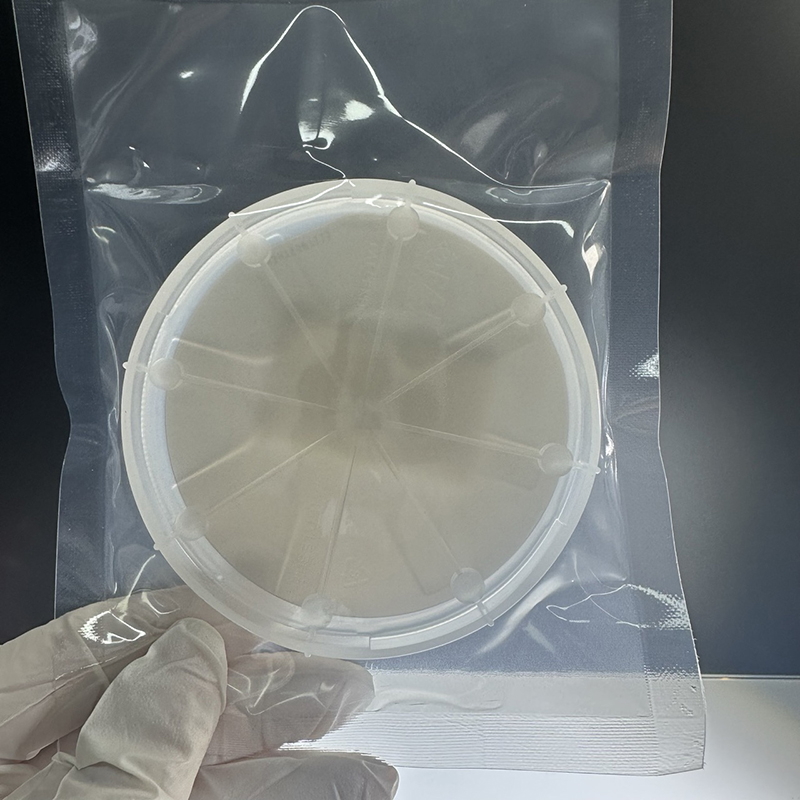

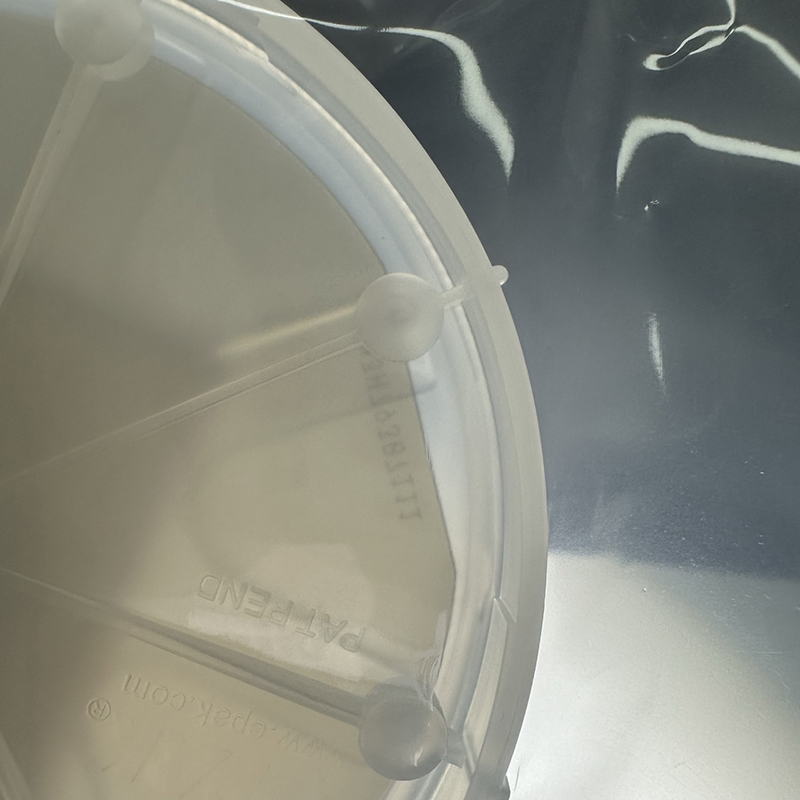

| Confezione | Cassetta multi-wafer o contenitore per wafer singolo | ||||||||||

Diagramma dettagliato

Prodotti correlati

Scrivi qui il tuo messaggio e inviacelo