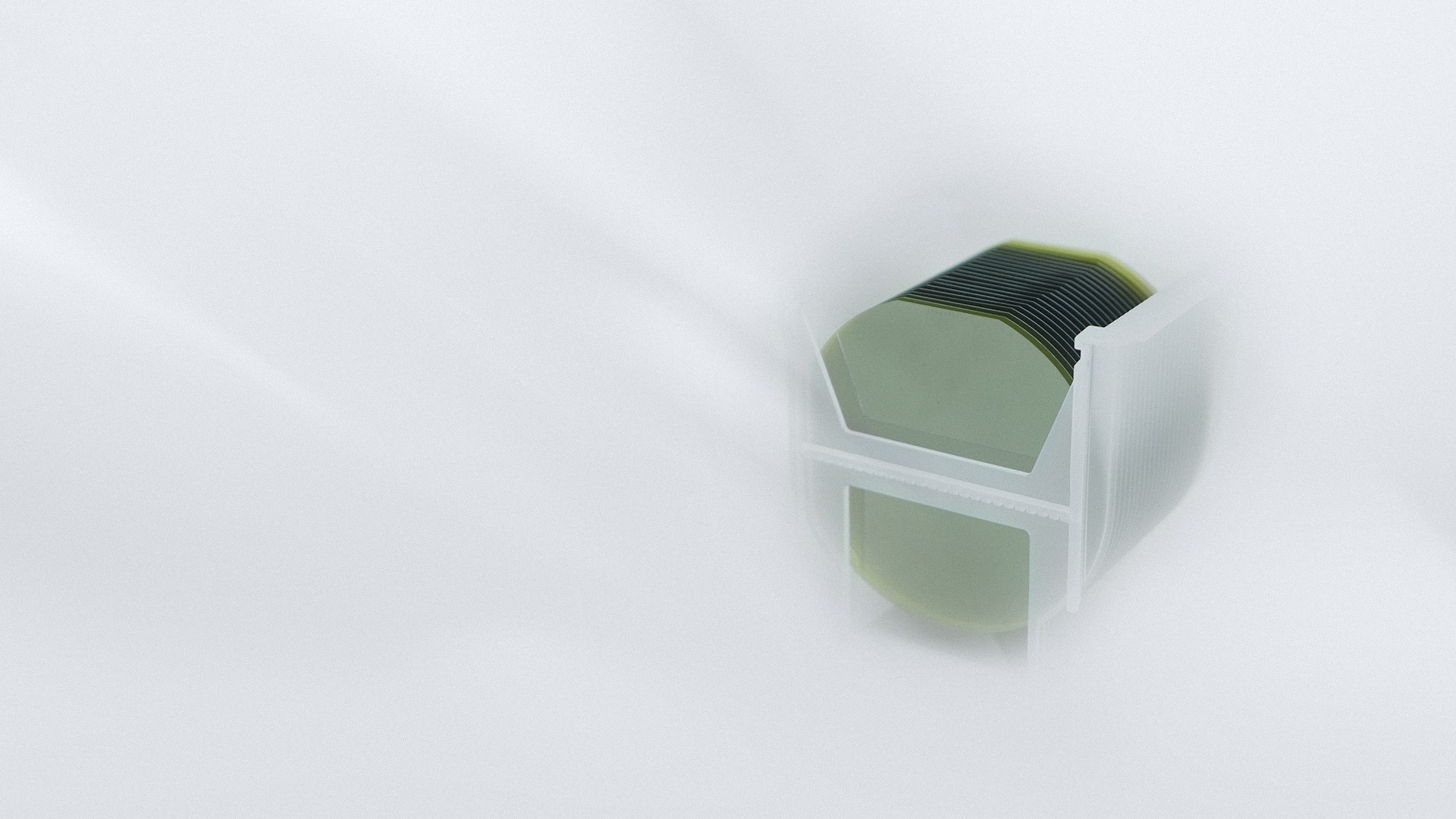

Wafer SiC HPSI 4H-N Wafer epitassiale SiC 6H-N 6H-P 3C-N per MOS o SBD

Breve descrizione del substrato SiC Epi-wafer SiC

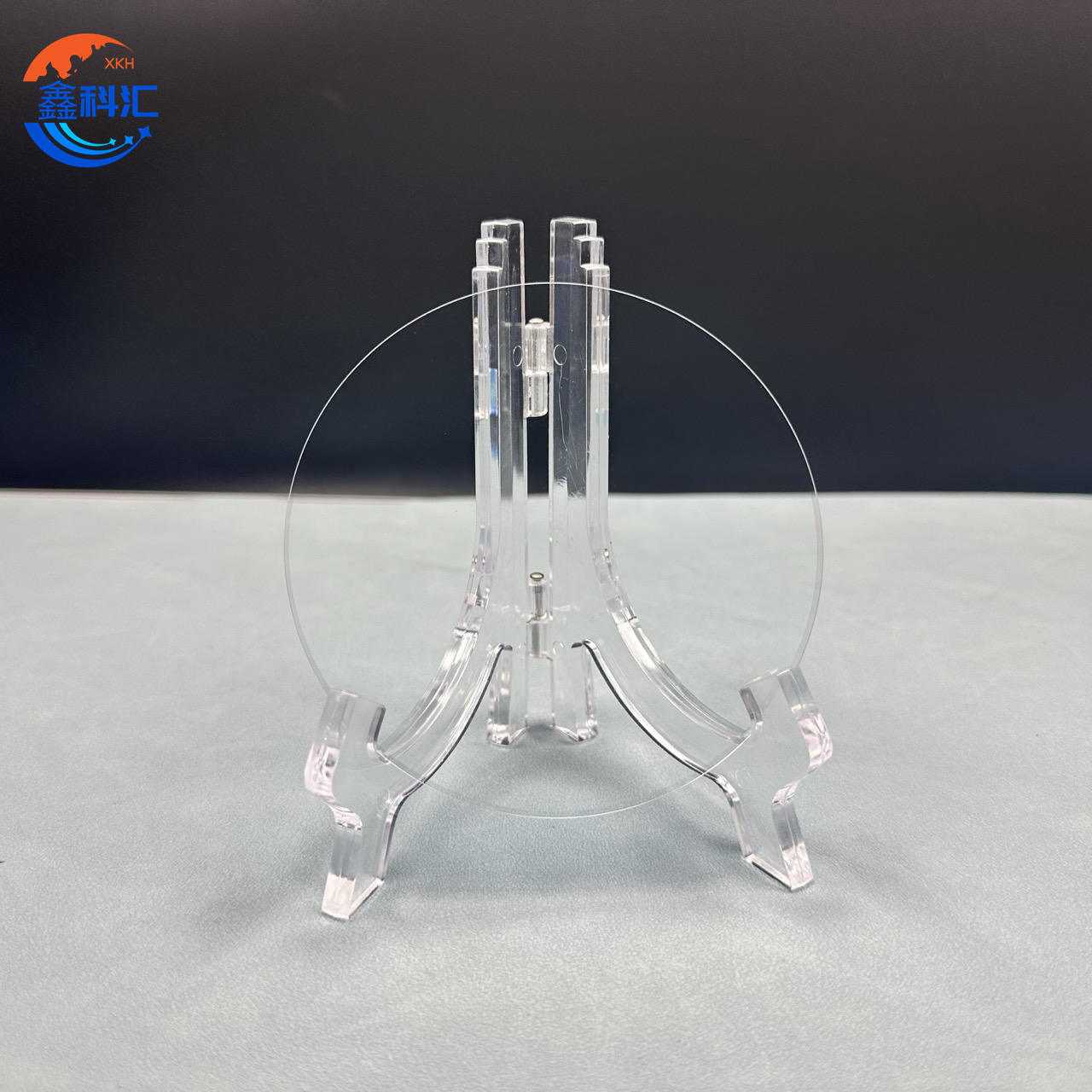

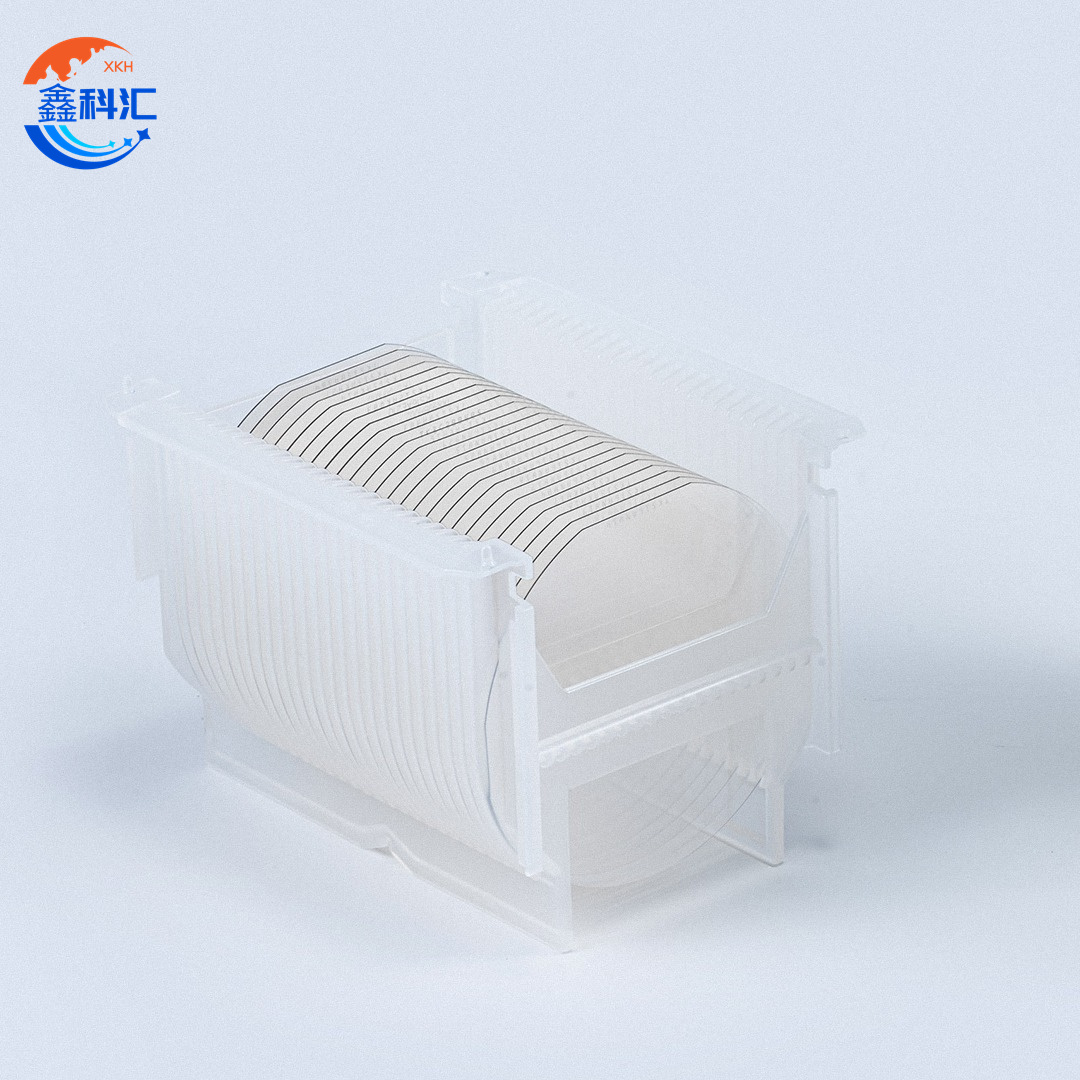

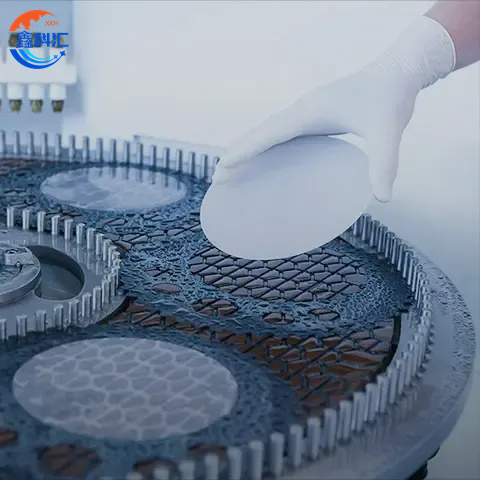

Offriamo un portafoglio completo di substrati e wafer in SiC di alta qualità in diversi politipi e profili di drogaggio, tra cui 4H-N (conduttivo di tipo n), 4H-P (conduttivo di tipo p), 4H-HPSI (semi-isolante ad alta purezza) e 6H-P (conduttivo di tipo p), in diametri da 4", 6" e 8" fino a 12". Oltre ai substrati nudi, i nostri servizi di crescita di wafer epi a valore aggiunto forniscono wafer epitassiali (epi) con spessore (1–20 µm), concentrazioni di drogaggio e densità dei difetti rigorosamente controllati.

Ogni wafer in SiC e wafer in Epi viene sottoposto a rigorosi controlli in linea (densità dei microtubi <0,1 cm², rugosità superficiale Ra <0,2 nm) e a una completa caratterizzazione elettrica (CV, mappatura della resistività) per garantire uniformità cristallina e prestazioni eccezionali. Che vengano utilizzati per moduli elettronici di potenza, amplificatori RF ad alta frequenza o dispositivi optoelettronici (LED, fotorilevatori), le nostre linee di prodotti per substrati in SiC e wafer in Epi offrono l'affidabilità, la stabilità termica e la resistenza alla rottura richieste dalle applicazioni più esigenti di oggi.

Proprietà e applicazione del substrato SiC di tipo 4H-N

-

Struttura politipica (esagonale) del substrato SiC 4H-N

L'ampio bandgap di ~3,26 eV garantisce prestazioni elettriche stabili e robustezza termica in condizioni di alta temperatura e campo elettrico elevato.

-

substrato di SiCDoping di tipo N

Il drogaggio con azoto controllato con precisione produce concentrazioni di portatori da 1×10¹⁶ a 1×10¹⁹ cm⁻³ e mobilità degli elettroni a temperatura ambiente fino a ~900 cm²/V·s, riducendo al minimo le perdite di conduzione.

-

substrato di SiCAmpia resistività e uniformità

Intervallo di resistività disponibile da 0,01 a 10 Ω·cm e spessori dei wafer da 350 a 650 µm con tolleranza del ±5% sia nel drogaggio che nello spessore, ideali per la fabbricazione di dispositivi ad alta potenza.

-

substrato di SiCDensità di difetti ultra bassa

Densità del microtubo < 0,1 cm⁻² e densità di dislocazione del piano basale < 500 cm⁻², con una resa del dispositivo > 99% e un'integrità cristallina superiore.

- substrato di SiCConduttività termica eccezionale

La conduttività termica fino a ~370 W/m·K facilita un'efficiente rimozione del calore, aumentando l'affidabilità del dispositivo e la densità di potenza.

-

substrato di SiCApplicazioni target

MOSFET SiC, diodi Schottky, moduli di potenza e dispositivi RF per azionamenti di veicoli elettrici, inverter solari, azionamenti industriali, sistemi di trazione e altri mercati esigenti dell'elettronica di potenza.

Specifiche del wafer SiC tipo 4H-N da 6 pollici | ||

| Proprietà | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

| Grado | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

| Diametro | 149,5 millimetri - 150,0 millimetri | 149,5 millimetri - 150,0 millimetri |

| Poli-tipo | 4H | 4H |

| Spessore | 350 µm ± 15 µm | 350 µm ± 25 µm |

| Orientamento del wafer | Fuori asse: 4,0° verso <1120> ± 0,5° | Fuori asse: 4,0° verso <1120> ± 0,5° |

| Densità del microtubo | ≤ 0,2 cm² | ≤ 15 cm² |

| Resistività | 0,015 - 0,024 Ω·cm | 0,015 - 0,028 Ω·cm |

| Orientamento primario piatto | [10-10] ± 50° | [10-10] ± 50° |

| Lunghezza piana primaria | 475 millimetri ± 2,0 millimetri | 475 millimetri ± 2,0 millimetri |

| Esclusione del bordo | 3 millimetri | 3 millimetri |

| LTV/TIV / Arco / Ordito | ≤ 2,5 µm / ≤ 6 µm / ≤ 25 µm / ≤ 35 µm | ≤ 5 µm / ≤ 15 µm / ≤ 40 µm / ≤ 60 µm |

| Rugosità | Ra polacco ≤ 1 nm | Ra polacco ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Crepe sui bordi causate da luce ad alta intensità | Lunghezza cumulativa ≤ 20 mm lunghezza singola ≤ 2 mm | Lunghezza cumulativa ≤ 20 mm lunghezza singola ≤ 2 mm |

| Piastre esagonali ad alta intensità luminosa | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 0,1% |

| Aree politipiche mediante luce ad alta intensità | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 3% |

| Inclusioni visive di carbonio | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 5% |

| Graffi sulla superficie del silicio causati dalla luce ad alta intensità | Lunghezza cumulativa ≤ 1 diametro del wafer | |

| Chip di bordo tramite luce ad alta intensità | Nessuno consentito ≥ 0,2 mm di larghezza e profondità | 7 consentiti, ≤ 1 mm ciascuno |

| Lussazione della vite filettata | < 500 cm³ | < 500 cm³ |

| Contaminazione della superficie del silicio da parte della luce ad alta intensità | ||

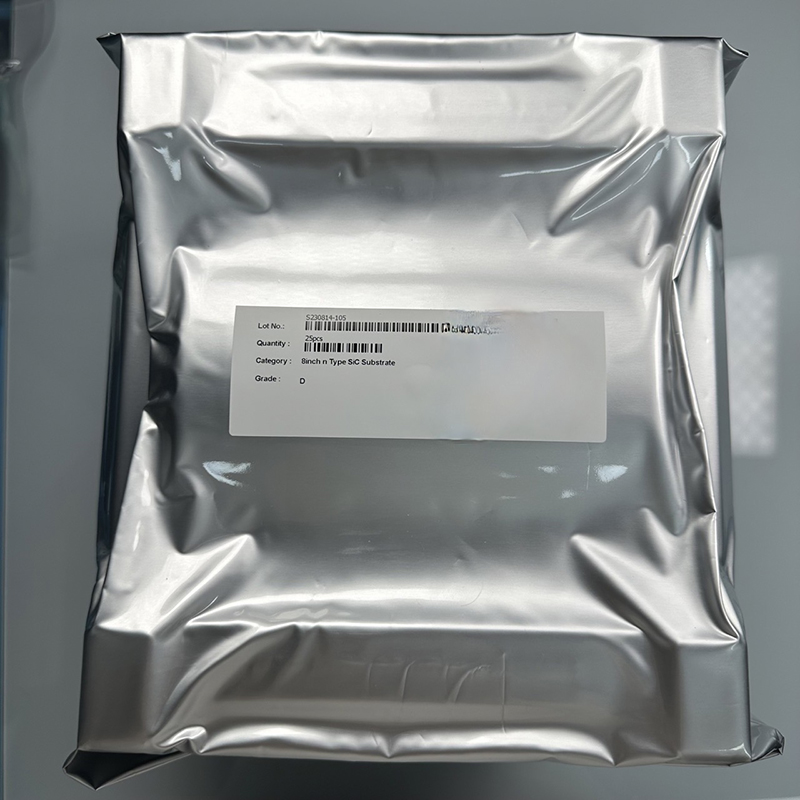

| Confezione | Cassetta multi-wafer o contenitore per wafer singolo | Cassetta multi-wafer o contenitore per wafer singolo |

Specifiche del wafer SiC tipo 4H-N da 8 pollici | ||

| Proprietà | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

| Grado | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

| Diametro | 199,5 millimetri - 200,0 millimetri | 199,5 millimetri - 200,0 millimetri |

| Poli-tipo | 4H | 4H |

| Spessore | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Orientamento del wafer | 4,0° verso <110> ± 0,5° | 4,0° verso <110> ± 0,5° |

| Densità del microtubo | ≤ 0,2 cm² | ≤ 5 cm² |

| Resistività | 0,015 - 0,025 Ω·cm | 0,015 - 0,028 Ω·cm |

| Orientamento Nobile | ||

| Esclusione del bordo | 3 millimetri | 3 millimetri |

| LTV/TIV / Arco / Ordito | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 70 µm | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 100 µm |

| Rugosità | Ra polacco ≤ 1 nm | Ra polacco ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Crepe sui bordi causate da luce ad alta intensità | Lunghezza cumulativa ≤ 20 mm lunghezza singola ≤ 2 mm | Lunghezza cumulativa ≤ 20 mm lunghezza singola ≤ 2 mm |

| Piastre esagonali ad alta intensità luminosa | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 0,1% |

| Aree politipiche mediante luce ad alta intensità | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 3% |

| Inclusioni visive di carbonio | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 5% |

| Graffi sulla superficie del silicio causati dalla luce ad alta intensità | Lunghezza cumulativa ≤ 1 diametro del wafer | |

| Chip di bordo tramite luce ad alta intensità | Nessuno consentito ≥ 0,2 mm di larghezza e profondità | 7 consentiti, ≤ 1 mm ciascuno |

| Lussazione della vite filettata | < 500 cm³ | < 500 cm³ |

| Contaminazione della superficie del silicio da parte della luce ad alta intensità | ||

| Confezione | Cassetta multi-wafer o contenitore per wafer singolo | Cassetta multi-wafer o contenitore per wafer singolo |

Il 4H-SiC è un materiale ad alte prestazioni utilizzato per l'elettronica di potenza, i dispositivi RF e le applicazioni ad alta temperatura. La sigla "4H" si riferisce alla struttura cristallina, che è esagonale, e la sigla "N" indica il tipo di drogaggio utilizzato per ottimizzare le prestazioni del materiale.

IL4H-SiCil tipo è comunemente utilizzato per:

Elettronica di potenza:Utilizzato in dispositivi come diodi, MOSFET e IGBT per gruppi propulsori di veicoli elettrici, macchinari industriali e sistemi di energia rinnovabile.

Tecnologia 5G:Considerata la richiesta di componenti ad alta frequenza e alta efficienza da parte del 5G, la capacità del SiC di gestire tensioni elevate e di funzionare ad alte temperature lo rende ideale per amplificatori di potenza delle stazioni base e dispositivi RF.

Sistemi di energia solare:Le eccellenti proprietà di gestione della potenza del SiC sono ideali per inverter e convertitori fotovoltaici (energia solare).

Veicoli elettrici (EV):Il SiC è ampiamente utilizzato nei gruppi propulsori dei veicoli elettrici per una conversione energetica più efficiente, una minore generazione di calore e densità di potenza più elevate.

Proprietà e applicazione del substrato SiC 4H di tipo semi-isolante

Proprietà:

-

Tecniche di controllo della densità senza microtubi: Garantisce l'assenza di microtubi, migliorando la qualità del substrato.

-

Tecniche di controllo monocristallino: Garantisce una struttura monocristallina per proprietà del materiale migliorate.

-

Tecniche di controllo delle inclusioni: Riduce al minimo la presenza di impurità o inclusioni, garantendo un substrato puro.

-

Tecniche di controllo della resistività: Consente un controllo preciso della resistività elettrica, fondamentale per le prestazioni del dispositivo.

-

Tecniche di regolazione e controllo delle impurità: Regola e limita l'introduzione di impurità per mantenere l'integrità del substrato.

-

Tecniche di controllo della larghezza del gradino del substrato: Fornisce un controllo accurato sulla larghezza del passo, garantendo la coerenza su tutto il substrato

Specifiche del substrato 4H-semi SiC da 6 pollici | ||

| Proprietà | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

| Diametro (mm) | 145 millimetri - 150 millimetri | 145 millimetri - 150 millimetri |

| Poli-tipo | 4H | 4H |

| Spessore (um) | 500 ± 15 | 500 ± 25 |

| Orientamento del wafer | Sull'asse: ±0,0001° | Sull'asse: ±0,05° |

| Densità del microtubo | ≤ 15 cm-2 | ≤ 15 cm-2 |

| Resistività (Ωcm) | ≥ 10E3 | ≥ 10E3 |

| Orientamento primario piatto | (0-10)° ± 5,0° | (10-10)° ± 5,0° |

| Lunghezza piana primaria | Tacca | Tacca |

| Esclusione del bordo (mm) | ≤ 2,5 µm / ≤ 15 µm | ≤ 5,5 µm / ≤ 35 µm |

| LTV / Ciotola / Ordito | ≤ 3 µm | ≤ 3 µm |

| Rugosità | Polacco Ra ≤ 1,5 µm | Polacco Ra ≤ 1,5 µm |

| Chip di bordo tramite luce ad alta intensità | ≤ 20 µm | ≤ 60 µm |

| Piastre riscaldanti ad alta intensità luminosa | Cumulativo ≤ 0,05% | Cumulativo ≤ 3% |

| Aree politipiche mediante luce ad alta intensità | Inclusioni di carbonio visive ≤ 0,05% | Cumulativo ≤ 3% |

| Graffi sulla superficie del silicio causati dalla luce ad alta intensità | ≤ 0,05% | Cumulativo ≤ 4% |

| Chip di bordo per luce ad alta intensità (dimensioni) | Non consentito > 02 mm di larghezza e profondità | Non consentito > 02 mm di larghezza e profondità |

| La dilatazione della vite di supporto | ≤ 500 µm | ≤ 500 µm |

| Contaminazione della superficie del silicio da parte della luce ad alta intensità | ≤ 1 x 10^5 | ≤ 1 x 10^5 |

| Confezione | Cassetta multi-wafer o contenitore per wafer singolo | Cassetta multi-wafer o contenitore per wafer singolo |

Specifiche del substrato SiC semiisolante 4H da 4 pollici

| Parametro | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

|---|---|---|

| Proprietà fisiche | ||

| Diametro | 99,5 millimetri – 100,0 millimetri | 99,5 millimetri – 100,0 millimetri |

| Poli-tipo | 4H | 4H |

| Spessore | 500 μm ± 15 μm | 500 μm ± 25 μm |

| Orientamento del wafer | Sull'asse: <600h > 0,5° | Sull'asse: <000h > 0,5° |

| Proprietà elettriche | ||

| Densità del microtubo (MPD) | ≤1 cm⁻² | ≤15 cm⁻² |

| Resistività | ≥150 Ω·cm | ≥1,5 Ω·cm |

| Tolleranze geometriche | ||

| Orientamento primario piatto | (0x10) ± 5,0° | (0x10) ± 5,0° |

| Lunghezza piana primaria | 52,5 millimetri ± 2,0 millimetri | 52,5 millimetri ± 2,0 millimetri |

| Lunghezza piatta secondaria | 18,0 millimetri ± 2,0 millimetri | 18,0 millimetri ± 2,0 millimetri |

| Orientamento secondario piatto | 90° CW da Prime piatto ± 5,0° (Si rivolto verso l'alto) | 90° CW da Prime piatto ± 5,0° (Si rivolto verso l'alto) |

| Esclusione del bordo | 3 millimetri | 3 millimetri |

| LTV / TTV / Prua / Ordito | ≤2,5 μm / ≤5 μm / ≤15 μm / ≤30 μm | ≤10 μm / ≤15 μm / ≤25 μm / ≤40 μm |

| Qualità della superficie | ||

| Rugosità superficiale (Polish Ra) | ≤1 nm | ≤1 nm |

| Rugosità superficiale (CMP Ra) | ≤0,2 nm | ≤0,2 nm |

| Crepe sui bordi (luce ad alta intensità) | Non consentito | Lunghezza cumulativa ≥10 mm, singola crepa ≤2 mm |

| Difetti della piastra esagonale | ≤0,05% area cumulativa | ≤0,1% area cumulativa |

| Aree di inclusione politipica | Non consentito | ≤1% area cumulativa |

| Inclusioni visive di carbonio | ≤0,05% area cumulativa | ≤1% area cumulativa |

| Graffi sulla superficie del silicio | Non consentito | ≤1 lunghezza cumulativa del diametro del wafer |

| Chip di bordo | Nessuno consentito (≥0,2 mm di larghezza/profondità) | ≤5 chip (ciascuno ≤1 mm) |

| Contaminazione della superficie del silicio | Non specificato | Non specificato |

| Confezione | ||

| Confezione | Cassetta multi-wafer o contenitore a wafer singolo | Cassetta multi-wafer o |

Applicazione:

ILSubstrati semi-isolanti SiC 4Hsono utilizzati principalmente in dispositivi elettronici ad alta potenza e alta frequenza, in particolare nelCampo RFQuesti substrati sono cruciali per varie applicazioni tra cuisistemi di comunicazione a microonde, radar a schiera di fase, Erilevatori elettrici senza filiLa loro elevata conduttività termica e le eccellenti caratteristiche elettriche li rendono ideali per applicazioni impegnative nei sistemi di elettronica di potenza e di comunicazione.

Proprietà e applicazione del wafer epi SiC tipo 4H-N

Proprietà e applicazioni dei wafer Epi di tipo SiC 4H-N

Proprietà del wafer Epi di tipo SiC 4H-N:

Composizione del materiale:

SiC (carburo di silicio): Noto per la sua eccezionale durezza, l'elevata conduttività termica e le eccellenti proprietà elettriche, il SiC è ideale per dispositivi elettronici ad alte prestazioni.

Politipo 4H-SiC: Il politipo 4H-SiC è noto per la sua elevata efficienza e stabilità nelle applicazioni elettroniche.

Doping di tipo N: Il drogaggio di tipo N (drogato con azoto) garantisce un'eccellente mobilità degli elettroni, rendendo il SiC adatto ad applicazioni ad alta frequenza e ad alta potenza.

Elevata conduttività termica:

I wafer SiC hanno una conduttività termica superiore, che in genere varia da120–200 W/m·K, consentendo loro di gestire efficacemente il calore in dispositivi ad alta potenza come transistor e diodi.

Ampio bandgap:

Con un bandgap di3,26 eV, 4H-SiC può funzionare a tensioni, frequenze e temperature più elevate rispetto ai tradizionali dispositivi basati sul silicio, il che lo rende ideale per applicazioni ad alta efficienza e alte prestazioni.

Proprietà elettriche:

L'elevata mobilità elettronica e la conduttività del SiC lo rendono ideale perelettronica di potenza, offrendo elevate velocità di commutazione e un'elevata capacità di gestione di corrente e tensione, con conseguenti sistemi di gestione dell'alimentazione più efficienti.

Resistenza meccanica e chimica:

Il SiC è uno dei materiali più duri, secondo solo al diamante, ed è altamente resistente all'ossidazione e alla corrosione, il che lo rende durevole in ambienti difficili.

Applicazioni del wafer Epi di tipo SiC 4H-N:

Elettronica di potenza:

I wafer epi di tipo SiC 4H-N sono ampiamente utilizzati inMOSFET di potenza, IGBT, Ediodiperconversione di potenzain sistemi comeinverter solari, veicoli elettrici, Esistemi di accumulo di energia, offrendo prestazioni migliorate ed efficienza energetica.

Veicoli elettrici (EV):

In gruppi propulsori per veicoli elettrici, controllori del motore, Estazioni di ricarica, i wafer SiC aiutano a ottenere una migliore efficienza della batteria, una ricarica più rapida e migliori prestazioni energetiche complessive grazie alla loro capacità di gestire potenze e temperature elevate.

Sistemi di energia rinnovabile:

Inverter solari: I wafer di SiC vengono utilizzati insistemi di energia solareper convertire l'energia CC dei pannelli solari in CA, aumentando l'efficienza e le prestazioni complessive del sistema.

Turbine eoliche: La tecnologia SiC è impiegata insistemi di controllo delle turbine eoliche, ottimizzando l'efficienza della generazione e della conversione di energia.

Aerospaziale e Difesa:

I wafer SiC sono ideali per l'uso inelettronica aerospazialeEapplicazioni militari, compresosistemi radarEelettronica satellitare, dove l'elevata resistenza alle radiazioni e la stabilità termica sono cruciali.

Applicazioni ad alta temperatura e alta frequenza:

I wafer di SiC eccellono inelettronica ad alta temperatura, utilizzato inmotori aeronautici, veicolo spaziale, Esistemi di riscaldamento industriale, poiché mantengono le prestazioni in condizioni di calore estremo. Inoltre, il loro ampio bandgap consente l'utilizzo inapplicazioni ad alta frequenzaPiacedispositivi RFEcomunicazioni a microonde.

| Specifiche assiali dell'epicentro di tipo N da 6 pollici | |||

| Parametro | unità | Z-MOS | |

| Tipo | Conduttività / Drogante | - | Tipo N / Azoto |

| strato tampone | Spessore dello strato tampone | um | 1 |

| Tolleranza dello spessore dello strato tampone | % | ±20% | |

| Concentrazione dello strato tampone | cm-3 | 1.00E+18 | |

| Tolleranza alla concentrazione dello strato tampone | % | ±20% | |

| 1° strato di Epi | Spessore dello strato di Epi | um | 11.5 |

| Uniformità dello spessore dello strato Epi | % | ±4% | |

| Tolleranza di spessore degli strati Epi ((Spec- Max, Min)/Specifica) | % | ±5% | |

| Concentrazione dello strato epi | cm-3 | 1E 15~ 1E 18 | |

| Tolleranza alla concentrazione dello strato epi | % | 6% | |

| Uniformità della concentrazione dello strato epi (σ /Significare) | % | ≤5% | |

| Uniformità della concentrazione dello strato Epi <(max-min)/(max+min> | % | ≤ 10% | |

| Forma del wafer epitassale | Arco | um | ≤±20 |

| ORDITO | um | ≤30 | |

| TTV | um | ≤ 10 | |

| LTV | um | ≤2 | |

| Caratteristiche generali | Lunghezza dei graffi | mm | ≤30mm |

| Chip di bordo | - | NESSUNO | |

| Definizione dei difetti | ≥97% (Misurato con 2*2, I difetti killer includono: I difetti includono Micropipe / Grandi noccioli, Carota, Triangolare | ||

| Contaminazione da metalli | atomi/cm² | d f f ll i ≤5E10 atomi/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca e Mn) | |

| Pacchetto | Specifiche di imballaggio | pezzi/scatola | cassetta multi-wafer o contenitore per wafer singolo |

| Specifiche epitassiali di tipo N da 8 pollici | |||

| Parametro | unità | Z-MOS | |

| Tipo | Conduttività / Drogante | - | Tipo N / Azoto |

| strato tampone | Spessore dello strato tampone | um | 1 |

| Tolleranza dello spessore dello strato tampone | % | ±20% | |

| Concentrazione dello strato tampone | cm-3 | 1.00E+18 | |

| Tolleranza alla concentrazione dello strato tampone | % | ±20% | |

| 1° strato di Epi | Spessore medio degli strati di Epi | um | 8~ 12 |

| Uniformità dello spessore degli strati Epi (σ/media) | % | ≤2.0 | |

| Tolleranza di spessore degli strati Epi ((Spec - Max,Min)/Spec) | % | ±6 | |

| Strati Epi Doping medio netto | cm-3 | 8E+15 ~2E+16 | |

| Uniformità netta del drogaggio degli strati Epi (σ/media) | % | ≤5 | |

| Tolleranza al drogaggio netto degli strati Epi ((Spec -Max, | % | ± 10,0 | |

| Forma del wafer epitassale | Mi )/S ) Ordito | um | ≤50,0 |

| Arco | um | ± 30,0 | |

| TTV | um | ≤ 10,0 | |

| LTV | um | ≤4,0 (10 mm × 10 mm) | |

| Generale Caratteristiche | Graffi | - | Lunghezza cumulativa ≤ 1/2diametro del wafer |

| Chip di bordo | - | ≤2 chip, ogni raggio ≤1,5 mm | |

| Contaminazione dei metalli superficiali | atomi/cm2 | ≤5E10 atomi/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca e Mn) | |

| Ispezione dei difetti | % | ≥ 96,0 (I difetti 2X2 includono microtubi/grandi fossette, Carota, Difetti triangolari, Cadute, Lineare/IGSF-s, BPD) | |

| Contaminazione dei metalli superficiali | atomi/cm2 | ≤5E10 atomi/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca e Mn) | |

| Pacchetto | Specifiche di imballaggio | - | cassetta multi-wafer o contenitore per wafer singolo |

Domande e risposte sui wafer SiC

D1: Quali sono i principali vantaggi dell'utilizzo di wafer SiC rispetto ai tradizionali wafer di silicio nell'elettronica di potenza?

A1:

I wafer SiC offrono diversi vantaggi chiave rispetto ai tradizionali wafer di silicio (Si) nell'elettronica di potenza, tra cui:

Maggiore efficienza: Il SiC ha un bandgap più ampio (3,26 eV) rispetto al silicio (1,1 eV), consentendo ai dispositivi di funzionare a tensioni, frequenze e temperature più elevate. Ciò si traduce in minori perdite di potenza e maggiore efficienza nei sistemi di conversione di potenza.

Alta conduttività termica: La conduttività termica del SiC è molto più elevata di quella del silicio, consentendo una migliore dissipazione del calore nelle applicazioni ad alta potenza, migliorando l'affidabilità e la durata dei dispositivi di potenza.

Gestione di tensioni e correnti più elevate:I dispositivi SiC possono gestire livelli di tensione e corrente più elevati, rendendoli adatti ad applicazioni ad alta potenza come veicoli elettrici, sistemi di energia rinnovabile e azionamenti di motori industriali.

Velocità di commutazione più rapida: I dispositivi SiC hanno capacità di commutazione più rapide, che contribuiscono a ridurre la perdita di energia e le dimensioni del sistema, rendendoli ideali per applicazioni ad alta frequenza.

D2: Quali sono le principali applicazioni dei wafer SiC nel settore automobilistico?

A2:

Nell'industria automobilistica, i wafer di SiC vengono utilizzati principalmente in:

Gruppi propulsori per veicoli elettrici (EV): Componenti basati su SiC comeinverterEMOSFET di potenzaMigliorare l'efficienza e le prestazioni dei gruppi propulsori dei veicoli elettrici consentendo velocità di commutazione più elevate e una maggiore densità energetica. Ciò si traduce in una maggiore durata della batteria e migliori prestazioni complessive del veicolo.

Caricabatterie di bordo:I dispositivi SiC contribuiscono a migliorare l'efficienza dei sistemi di ricarica di bordo consentendo tempi di ricarica più rapidi e una migliore gestione termica, fondamentale affinché i veicoli elettrici possano supportare stazioni di ricarica ad alta potenza.

Sistemi di gestione della batteria (BMS): La tecnologia SiC migliora l'efficienza disistemi di gestione della batteria, consentendo una migliore regolazione della tensione, una maggiore gestione della potenza e una maggiore durata della batteria.

Convertitori CC-CC: I wafer di SiC vengono utilizzati inConvertitori CC-CCper convertire in modo più efficiente l'energia CC ad alta tensione in energia CC a bassa tensione, il che è fondamentale nei veicoli elettrici per gestire l'energia dalla batteria ai vari componenti del veicolo.

Le prestazioni superiori del SiC nelle applicazioni ad alta tensione, alta temperatura e alta efficienza lo rendono essenziale per la transizione dell'industria automobilistica verso la mobilità elettrica.

Specifiche del wafer SiC tipo 4H-N da 6 pollici | ||

| Proprietà | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

| Grado | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

| Diametro | 149,5 millimetri – 150,0 millimetri | 149,5 millimetri – 150,0 millimetri |

| Poli-tipo | 4H | 4H |

| Spessore | 350 µm ± 15 µm | 350 µm ± 25 µm |

| Orientamento del wafer | Fuori asse: 4,0° verso <1120> ± 0,5° | Fuori asse: 4,0° verso <1120> ± 0,5° |

| Densità del microtubo | ≤ 0,2 cm² | ≤ 15 cm² |

| Resistività | 0,015 – 0,024 Ω·cm | 0,015 – 0,028 Ω·cm |

| Orientamento primario piatto | [10-10] ± 50° | [10-10] ± 50° |

| Lunghezza piana primaria | 475 millimetri ± 2,0 millimetri | 475 millimetri ± 2,0 millimetri |

| Esclusione del bordo | 3 millimetri | 3 millimetri |

| LTV/TIV / Arco / Ordito | ≤ 2,5 µm / ≤ 6 µm / ≤ 25 µm / ≤ 35 µm | ≤ 5 µm / ≤ 15 µm / ≤ 40 µm / ≤ 60 µm |

| Rugosità | Ra polacco ≤ 1 nm | Ra polacco ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Crepe sui bordi causate da luce ad alta intensità | Lunghezza cumulativa ≤ 20 mm lunghezza singola ≤ 2 mm | Lunghezza cumulativa ≤ 20 mm lunghezza singola ≤ 2 mm |

| Piastre esagonali ad alta intensità luminosa | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 0,1% |

| Aree politipiche mediante luce ad alta intensità | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 3% |

| Inclusioni visive di carbonio | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 5% |

| Graffi sulla superficie del silicio causati dalla luce ad alta intensità | Lunghezza cumulativa ≤ 1 diametro del wafer | |

| Chip di bordo tramite luce ad alta intensità | Nessuno consentito ≥ 0,2 mm di larghezza e profondità | 7 consentiti, ≤ 1 mm ciascuno |

| Lussazione della vite filettata | < 500 cm³ | < 500 cm³ |

| Contaminazione della superficie del silicio da parte della luce ad alta intensità | ||

| Confezione | Cassetta multi-wafer o contenitore per wafer singolo | Cassetta multi-wafer o contenitore per wafer singolo |

Specifiche del wafer SiC tipo 4H-N da 8 pollici | ||

| Proprietà | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

| Grado | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

| Diametro | 199,5 millimetri – 200,0 millimetri | 199,5 millimetri – 200,0 millimetri |

| Poli-tipo | 4H | 4H |

| Spessore | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Orientamento del wafer | 4,0° verso <110> ± 0,5° | 4,0° verso <110> ± 0,5° |

| Densità del microtubo | ≤ 0,2 cm² | ≤ 5 cm² |

| Resistività | 0,015 – 0,025 Ω·cm | 0,015 – 0,028 Ω·cm |

| Orientamento Nobile | ||

| Esclusione del bordo | 3 millimetri | 3 millimetri |

| LTV/TIV / Arco / Ordito | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 70 µm | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 100 µm |

| Rugosità | Ra polacco ≤ 1 nm | Ra polacco ≤ 1 nm |

| CMP Ra | ≤ 0,2 nm | ≤ 0,5 nm |

| Crepe sui bordi causate da luce ad alta intensità | Lunghezza cumulativa ≤ 20 mm lunghezza singola ≤ 2 mm | Lunghezza cumulativa ≤ 20 mm lunghezza singola ≤ 2 mm |

| Piastre esagonali ad alta intensità luminosa | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 0,1% |

| Aree politipiche mediante luce ad alta intensità | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 3% |

| Inclusioni visive di carbonio | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 5% |

| Graffi sulla superficie del silicio causati dalla luce ad alta intensità | Lunghezza cumulativa ≤ 1 diametro del wafer | |

| Chip di bordo tramite luce ad alta intensità | Nessuno consentito ≥ 0,2 mm di larghezza e profondità | 7 consentiti, ≤ 1 mm ciascuno |

| Lussazione della vite filettata | < 500 cm³ | < 500 cm³ |

| Contaminazione della superficie del silicio da parte della luce ad alta intensità | ||

| Confezione | Cassetta multi-wafer o contenitore per wafer singolo | Cassetta multi-wafer o contenitore per wafer singolo |

Specifiche del substrato 4H-semi SiC da 6 pollici | ||

| Proprietà | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

| Diametro (mm) | 145 millimetri – 150 millimetri | 145 millimetri – 150 millimetri |

| Poli-tipo | 4H | 4H |

| Spessore (um) | 500 ± 15 | 500 ± 25 |

| Orientamento del wafer | Sull'asse: ±0,0001° | Sull'asse: ±0,05° |

| Densità del microtubo | ≤ 15 cm-2 | ≤ 15 cm-2 |

| Resistività (Ωcm) | ≥ 10E3 | ≥ 10E3 |

| Orientamento primario piatto | (0-10)° ± 5,0° | (10-10)° ± 5,0° |

| Lunghezza piana primaria | Tacca | Tacca |

| Esclusione del bordo (mm) | ≤ 2,5 µm / ≤ 15 µm | ≤ 5,5 µm / ≤ 35 µm |

| LTV / Ciotola / Ordito | ≤ 3 µm | ≤ 3 µm |

| Rugosità | Polacco Ra ≤ 1,5 µm | Polacco Ra ≤ 1,5 µm |

| Chip di bordo tramite luce ad alta intensità | ≤ 20 µm | ≤ 60 µm |

| Piastre riscaldanti ad alta intensità luminosa | Cumulativo ≤ 0,05% | Cumulativo ≤ 3% |

| Aree politipiche mediante luce ad alta intensità | Inclusioni di carbonio visive ≤ 0,05% | Cumulativo ≤ 3% |

| Graffi sulla superficie del silicio causati dalla luce ad alta intensità | ≤ 0,05% | Cumulativo ≤ 4% |

| Chip di bordo per luce ad alta intensità (dimensioni) | Non consentito > 02 mm di larghezza e profondità | Non consentito > 02 mm di larghezza e profondità |

| La dilatazione della vite di supporto | ≤ 500 µm | ≤ 500 µm |

| Contaminazione della superficie del silicio da parte della luce ad alta intensità | ≤ 1 x 10^5 | ≤ 1 x 10^5 |

| Confezione | Cassetta multi-wafer o contenitore per wafer singolo | Cassetta multi-wafer o contenitore per wafer singolo |

Specifiche del substrato SiC semiisolante 4H da 4 pollici

| Parametro | Grado di produzione Zero MPD (grado Z) | Grado fittizio (grado D) |

|---|---|---|

| Proprietà fisiche | ||

| Diametro | 99,5 millimetri – 100,0 millimetri | 99,5 millimetri – 100,0 millimetri |

| Poli-tipo | 4H | 4H |

| Spessore | 500 μm ± 15 μm | 500 μm ± 25 μm |

| Orientamento del wafer | Sull'asse: <600h > 0,5° | Sull'asse: <000h > 0,5° |

| Proprietà elettriche | ||

| Densità del microtubo (MPD) | ≤1 cm⁻² | ≤15 cm⁻² |

| Resistività | ≥150 Ω·cm | ≥1,5 Ω·cm |

| Tolleranze geometriche | ||

| Orientamento primario piatto | (0×10) ± 5,0° | (0×10) ± 5,0° |

| Lunghezza piana primaria | 52,5 millimetri ± 2,0 millimetri | 52,5 millimetri ± 2,0 millimetri |

| Lunghezza piatta secondaria | 18,0 millimetri ± 2,0 millimetri | 18,0 millimetri ± 2,0 millimetri |

| Orientamento secondario piatto | 90° CW da Prime piatto ± 5,0° (Si rivolto verso l'alto) | 90° CW da Prime piatto ± 5,0° (Si rivolto verso l'alto) |

| Esclusione del bordo | 3 millimetri | 3 millimetri |

| LTV / TTV / Prua / Ordito | ≤2,5 μm / ≤5 μm / ≤15 μm / ≤30 μm | ≤10 μm / ≤15 μm / ≤25 μm / ≤40 μm |

| Qualità della superficie | ||

| Rugosità superficiale (Polish Ra) | ≤1 nm | ≤1 nm |

| Rugosità superficiale (CMP Ra) | ≤0,2 nm | ≤0,2 nm |

| Crepe sui bordi (luce ad alta intensità) | Non consentito | Lunghezza cumulativa ≥10 mm, singola crepa ≤2 mm |

| Difetti della piastra esagonale | ≤0,05% area cumulativa | ≤0,1% area cumulativa |

| Aree di inclusione politipica | Non consentito | ≤1% area cumulativa |

| Inclusioni visive di carbonio | ≤0,05% area cumulativa | ≤1% area cumulativa |

| Graffi sulla superficie del silicio | Non consentito | ≤1 lunghezza cumulativa del diametro del wafer |

| Chip di bordo | Nessuno consentito (≥0,2 mm di larghezza/profondità) | ≤5 chip (ciascuno ≤1 mm) |

| Contaminazione della superficie del silicio | Non specificato | Non specificato |

| Confezione | ||

| Confezione | Cassetta multi-wafer o contenitore a wafer singolo | Cassetta multi-wafer o |

| Specifiche assiali dell'epicentro di tipo N da 6 pollici | |||

| Parametro | unità | Z-MOS | |

| Tipo | Conduttività / Drogante | - | Tipo N / Azoto |

| strato tampone | Spessore dello strato tampone | um | 1 |

| Tolleranza dello spessore dello strato tampone | % | ±20% | |

| Concentrazione dello strato tampone | cm-3 | 1.00E+18 | |

| Tolleranza alla concentrazione dello strato tampone | % | ±20% | |

| 1° strato di Epi | Spessore dello strato di Epi | um | 11.5 |

| Uniformità dello spessore dello strato Epi | % | ±4% | |

| Tolleranza di spessore degli strati Epi ((Spec- Max, Min)/Specifica) | % | ±5% | |

| Concentrazione dello strato epi | cm-3 | 1E 15~ 1E 18 | |

| Tolleranza alla concentrazione dello strato epi | % | 6% | |

| Uniformità della concentrazione dello strato epi (σ /Significare) | % | ≤5% | |

| Uniformità della concentrazione dello strato Epi <(max-min)/(max+min> | % | ≤ 10% | |

| Forma del wafer epitassale | Arco | um | ≤±20 |

| ORDITO | um | ≤30 | |

| TTV | um | ≤ 10 | |

| LTV | um | ≤2 | |

| Caratteristiche generali | Lunghezza dei graffi | mm | ≤30mm |

| Chip di bordo | - | NESSUNO | |

| Definizione dei difetti | ≥97% (Misurato con 2*2, I difetti killer includono: I difetti includono Micropipe / Grandi noccioli, Carota, Triangolare | ||

| Contaminazione da metalli | atomi/cm² | d f f ll i ≤5E10 atomi/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca e Mn) | |

| Pacchetto | Specifiche di imballaggio | pezzi/scatola | cassetta multi-wafer o contenitore per wafer singolo |

| Specifiche epitassiali di tipo N da 8 pollici | |||

| Parametro | unità | Z-MOS | |

| Tipo | Conduttività / Drogante | - | Tipo N / Azoto |

| strato tampone | Spessore dello strato tampone | um | 1 |

| Tolleranza dello spessore dello strato tampone | % | ±20% | |

| Concentrazione dello strato tampone | cm-3 | 1.00E+18 | |

| Tolleranza alla concentrazione dello strato tampone | % | ±20% | |

| 1° strato di Epi | Spessore medio degli strati di Epi | um | 8~ 12 |

| Uniformità dello spessore degli strati Epi (σ/media) | % | ≤2.0 | |

| Tolleranza di spessore degli strati Epi ((Spec - Max,Min)/Spec) | % | ±6 | |

| Strati Epi Doping medio netto | cm-3 | 8E+15 ~2E+16 | |

| Uniformità netta del drogaggio degli strati Epi (σ/media) | % | ≤5 | |

| Tolleranza al drogaggio netto degli strati Epi ((Spec -Max, | % | ± 10,0 | |

| Forma del wafer epitassale | Mi )/S ) Ordito | um | ≤50,0 |

| Arco | um | ± 30,0 | |

| TTV | um | ≤ 10,0 | |

| LTV | um | ≤4,0 (10 mm × 10 mm) | |

| Generale Caratteristiche | Graffi | - | Lunghezza cumulativa ≤ 1/2diametro del wafer |

| Chip di bordo | - | ≤2 chip, ogni raggio ≤1,5 mm | |

| Contaminazione dei metalli superficiali | atomi/cm2 | ≤5E10 atomi/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca e Mn) | |

| Ispezione dei difetti | % | ≥ 96,0 (I difetti 2X2 includono microtubi/grandi fossette, Carota, Difetti triangolari, Cadute, Lineare/IGSF-s, BPD) | |

| Contaminazione dei metalli superficiali | atomi/cm2 | ≤5E10 atomi/cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca e Mn) | |

| Pacchetto | Specifiche di imballaggio | - | cassetta multi-wafer o contenitore per wafer singolo |

D1: Quali sono i principali vantaggi dell'utilizzo di wafer SiC rispetto ai tradizionali wafer di silicio nell'elettronica di potenza?

A1:

I wafer SiC offrono diversi vantaggi chiave rispetto ai tradizionali wafer di silicio (Si) nell'elettronica di potenza, tra cui:

Maggiore efficienza: Il SiC ha un bandgap più ampio (3,26 eV) rispetto al silicio (1,1 eV), consentendo ai dispositivi di funzionare a tensioni, frequenze e temperature più elevate. Ciò si traduce in minori perdite di potenza e maggiore efficienza nei sistemi di conversione di potenza.

Alta conduttività termica: La conduttività termica del SiC è molto più elevata di quella del silicio, consentendo una migliore dissipazione del calore nelle applicazioni ad alta potenza, migliorando l'affidabilità e la durata dei dispositivi di potenza.

Gestione di tensioni e correnti più elevate:I dispositivi SiC possono gestire livelli di tensione e corrente più elevati, rendendoli adatti ad applicazioni ad alta potenza come veicoli elettrici, sistemi di energia rinnovabile e azionamenti di motori industriali.

Velocità di commutazione più rapida: I dispositivi SiC hanno capacità di commutazione più rapide, che contribuiscono a ridurre la perdita di energia e le dimensioni del sistema, rendendoli ideali per applicazioni ad alta frequenza.

D2: Quali sono le principali applicazioni dei wafer SiC nel settore automobilistico?

A2:

Nell'industria automobilistica, i wafer di SiC vengono utilizzati principalmente in:

Gruppi propulsori per veicoli elettrici (EV): Componenti basati su SiC comeinverterEMOSFET di potenzaMigliorare l'efficienza e le prestazioni dei gruppi propulsori dei veicoli elettrici consentendo velocità di commutazione più elevate e una maggiore densità energetica. Ciò si traduce in una maggiore durata della batteria e migliori prestazioni complessive del veicolo.

Caricabatterie di bordo:I dispositivi SiC contribuiscono a migliorare l'efficienza dei sistemi di ricarica di bordo consentendo tempi di ricarica più rapidi e una migliore gestione termica, fondamentale affinché i veicoli elettrici possano supportare stazioni di ricarica ad alta potenza.

Sistemi di gestione della batteria (BMS): La tecnologia SiC migliora l'efficienza disistemi di gestione della batteria, consentendo una migliore regolazione della tensione, una maggiore gestione della potenza e una maggiore durata della batteria.

Convertitori CC-CC: I wafer di SiC vengono utilizzati inConvertitori CC-CCper convertire in modo più efficiente l'energia CC ad alta tensione in energia CC a bassa tensione, il che è fondamentale nei veicoli elettrici per gestire l'energia dalla batteria ai vari componenti del veicolo.

Le prestazioni superiori del SiC nelle applicazioni ad alta tensione, alta temperatura e alta efficienza lo rendono essenziale per la transizione dell'industria automobilistica verso la mobilità elettrica.