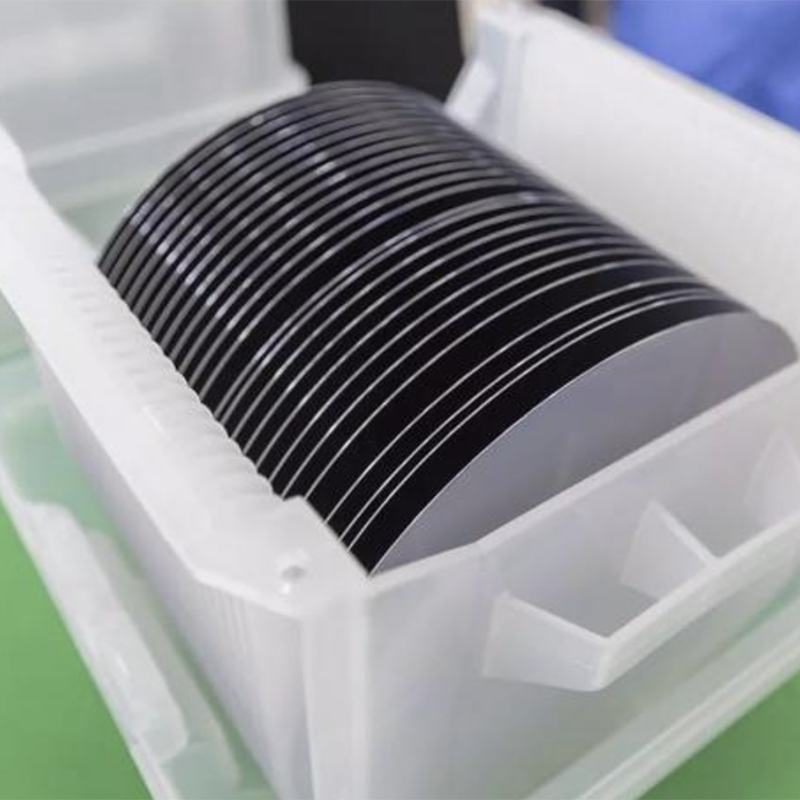

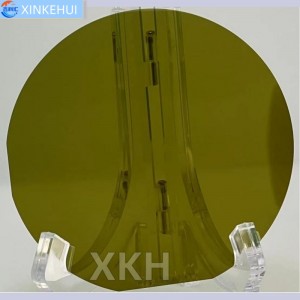

Wafer epitassiale SiC per dispositivi di potenza – 4H-SiC, tipo N, bassa densità di difetti

Diagramma dettagliato

Introduzione

Il wafer epitassiale in SiC è il cuore dei moderni dispositivi a semiconduttore ad alte prestazioni, in particolare quelli progettati per operazioni ad alta potenza, alta frequenza e alta temperatura. Abbreviazione di Silicon Carbide Epitaxi Wafer, un wafer epitassiale in SiC è costituito da uno strato epitassiale in SiC sottile e di alta qualità, sviluppato su un substrato di SiC bulk. L'uso della tecnologia dei wafer epitassiali in SiC si sta rapidamente espandendo nei veicoli elettrici, nelle reti intelligenti, nei sistemi di energia rinnovabile e nel settore aerospaziale grazie alle sue proprietà fisiche ed elettroniche superiori rispetto ai wafer convenzionali a base di silicio.

Principi di fabbricazione del wafer epitassiale SiC

La creazione di un wafer epitassiale in SiC richiede un processo di deposizione chimica da vapore (CVD) altamente controllato. Lo strato epitassiale viene in genere coltivato su un substrato di SiC monocristallino utilizzando gas come silano (SiH₄), propano (C₃H₈) e idrogeno (H₂) a temperature superiori a 1500 °C. Questa crescita epitassiale ad alta temperatura garantisce un eccellente allineamento cristallino e difetti minimi tra lo strato epitassiale e il substrato.

Il processo comprende diverse fasi chiave:

-

Preparazione del substrato: Il wafer di base in SiC viene pulito e lucidato fino a raggiungere la levigatezza atomica.

-

Crescita delle malattie cardiovascolari: In un reattore ad alta purezza, i gas reagiscono depositando uno strato monocristallino di SiC sul substrato.

-

Controllo antidoping: Durante l'epitassia viene introdotto il drogaggio di tipo N o di tipo P per ottenere le proprietà elettriche desiderate.

-

Ispezione e metrologia: Per verificare lo spessore dello strato, la concentrazione del drogaggio e la densità dei difetti vengono utilizzati la microscopia ottica, l'AFM e la diffrazione dei raggi X.

Ogni wafer epitassiale in SiC viene attentamente monitorato per mantenere tolleranze rigorose in termini di uniformità di spessore, planarità superficiale e resistività. La capacità di regolare con precisione questi parametri è essenziale per MOSFET ad alta tensione, diodi Schottky e altri dispositivi di potenza.

Specifica

| Parametro | Specifica |

| Categorie | Scienza dei materiali, substrati monocristallini |

| Politipo | 4H |

| Doping | Tipo N |

| Diametro | 101 millimetri |

| Tolleranza del diametro | ± 5% |

| Spessore | 0,35 millimetri |

| Tolleranza di spessore | ± 5% |

| Lunghezza piana primaria | 22 millimetri (± 10%) |

| TTV (variazione dello spessore totale) | ≤10 µm |

| Ordito | ≤25 µm |

| FWHM | ≤30 secondi d'arco |

| Finitura superficiale | Rq ≤0,35 nm |

Applicazioni del wafer epitassiale SiC

I prodotti SiC Epitaxi Wafer sono indispensabili in molteplici settori:

-

Veicoli elettrici (EV): I dispositivi basati su wafer epitassiali SiC aumentano l'efficienza del gruppo propulsore e riducono il peso.

-

Energia rinnovabile: Utilizzato negli inverter per impianti solari ed eolici.

-

Alimentatori industriali: Consente la commutazione ad alta frequenza e alta temperatura con perdite ridotte.

-

Aerospaziale e difesa: Ideale per ambienti difficili che richiedono semiconduttori robusti.

-

Stazioni base 5G: I componenti dei wafer epitassiali SiC supportano densità di potenza più elevate per applicazioni RF.

Il wafer epitassiale SiC consente design compatti, commutazione più rapida e maggiore efficienza di conversione energetica rispetto ai wafer di silicio.

Vantaggi del wafer epitassiale SiC

La tecnologia dei wafer epitassiali SiC offre notevoli vantaggi:

-

Alta tensione di rottura: Resiste a tensioni fino a 10 volte superiori rispetto ai wafer di Si.

-

Conduttività termica: Il wafer epitassiale SiC dissipa il calore più velocemente, consentendo ai dispositivi di funzionare a temperature più basse e in modo più affidabile.

-

Elevate velocità di commutazione: Le minori perdite di commutazione consentono una maggiore efficienza e miniaturizzazione.

-

Ampio bandgap: Garantisce stabilità a tensioni e temperature più elevate.

-

Robustezza del materiale: Il SiC è chimicamente inerte e meccanicamente resistente, ideale per applicazioni impegnative.

Questi vantaggi rendono il wafer epitassiale SiC il materiale di scelta per la prossima generazione di semiconduttori.

FAQ: Wafer epitassiale SiC

D1: Qual è la differenza tra un wafer SiC e un wafer epitassiale SiC?

Un wafer SiC si riferisce al substrato in massa, mentre un wafer epitassiale SiC include uno strato drogato appositamente sviluppato utilizzato nella fabbricazione del dispositivo.

D2: Quali spessori sono disponibili per gli strati di wafer epitassiali in SiC?

Gli strati epitassiali variano in genere da pochi micrometri a oltre 100 μm, a seconda dei requisiti applicativi.

D3: Il wafer epitassiale in SiC è adatto ad ambienti ad alta temperatura?

Sì, il wafer epitassiale SiC può funzionare in condizioni superiori a 600°C, superando significativamente le prestazioni del silicio.

D4: Perché la densità dei difetti è importante nei wafer epitassiali in SiC?

Una minore densità di difetti migliora le prestazioni e la resa del dispositivo, soprattutto nelle applicazioni ad alta tensione.

D5: Sono disponibili sia wafer epitassiali SiC di tipo N che di tipo P?

Sì, entrambi i tipi vengono prodotti utilizzando un controllo preciso del gas drogante durante il processo epitassiale.

D6: Quali sono le dimensioni standard dei wafer epitassiali in SiC?

I diametri standard includono 2 pollici, 4 pollici, 6 pollici e, sempre più, 8 pollici per la produzione su larga scala.

D7: In che modo il wafer epitassiale in SiC influisce sui costi e sull'efficienza?

Sebbene inizialmente più costoso del silicio, il wafer epitassiale in SiC riduce le dimensioni del sistema e la perdita di potenza, migliorando l'efficienza dei costi totali nel lungo termine.