La tecnologia di wafer dicing, fase fondamentale del processo di produzione dei semiconduttori, è direttamente collegata alle prestazioni, alla resa e ai costi di produzione dei chip.

#01 Contesto e significato del taglio a cubetti delle cialde

1.1 Definizione di Wafer Dicing

Il wafer dicing (noto anche come scribing) è una fase essenziale nella produzione di semiconduttori, volta a suddividere i wafer lavorati in più die individuali. Questi die contengono tipicamente funzionalità circuitali complete e sono i componenti principali utilizzati nella produzione di dispositivi elettronici. Con la crescente complessità dei progetti di chip e la continua riduzione delle dimensioni, i requisiti di precisione ed efficienza per la tecnologia di wafer dicing stanno diventando sempre più rigorosi.

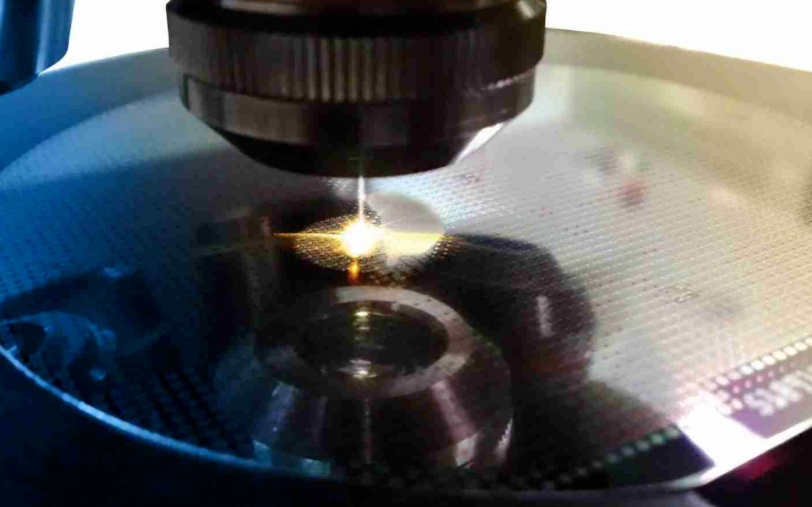

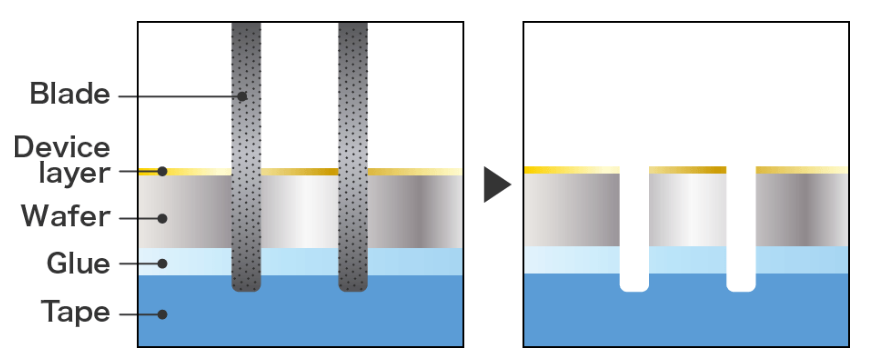

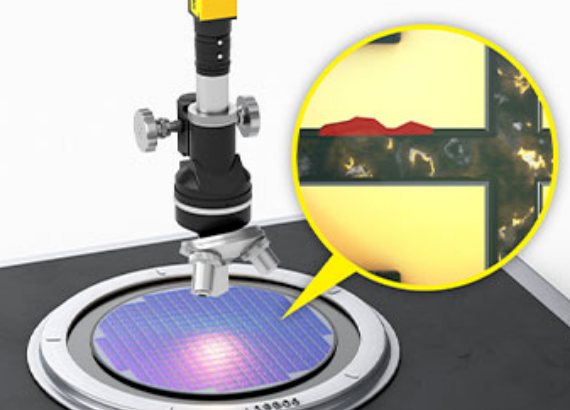

Nelle operazioni pratiche, la lavorazione dei wafer utilizza in genere utensili ad alta precisione, come lame diamantate, per garantire che ogni matrice rimanga intatta e perfettamente funzionante. I passaggi chiave includono la preparazione prima del taglio, il controllo preciso durante il processo di taglio e l'ispezione di qualità dopo il taglio.

Prima del taglio, il wafer deve essere marcato e posizionato per garantire percorsi di taglio precisi. Durante il taglio, parametri come la pressione e la velocità dell'utensile devono essere rigorosamente controllati per evitare danni al wafer. Dopo il taglio, vengono eseguiti controlli di qualità approfonditi per garantire che ogni chip soddisfi gli standard prestazionali.

I principi fondamentali della tecnologia di taglio a cubetti di wafer comprendono non solo la selezione dell'attrezzatura di taglio e l'impostazione dei parametri di processo, ma anche l'influenza delle proprietà meccaniche e delle caratteristiche dei materiali sulla qualità del taglio. Ad esempio, i wafer di silicio dielettrici a bassa k, a causa delle loro inferiori proprietà meccaniche, sono altamente suscettibili alla concentrazione di stress durante il taglio, causando guasti come scheggiature e cricche. La bassa durezza e fragilità dei materiali a bassa k li rendono più soggetti a danni strutturali sotto sforzo meccanico o termico, in particolare durante il taglio. Il contatto tra l'utensile e la superficie del wafer, unito alle alte temperature, può ulteriormente aggravare la concentrazione di stress.

Con i progressi nella scienza dei materiali, la tecnologia di taglio a dadini dei wafer si è espansa oltre i tradizionali semiconduttori a base di silicio, includendo nuovi materiali come il nitruro di gallio (GaN). Questi nuovi materiali, grazie alla loro durezza e alle loro proprietà strutturali, pongono nuove sfide ai processi di taglio, richiedendo ulteriori miglioramenti negli utensili e nelle tecniche di taglio.

In quanto processo critico nel settore dei semiconduttori, il wafer dicing continua a essere ottimizzato in risposta alle crescenti esigenze e ai progressi tecnologici, gettando le basi per le future tecnologie della microelettronica e dei circuiti integrati.

I miglioramenti nella tecnologia di wafer dicing vanno oltre lo sviluppo di materiali e utensili ausiliari. Comprendono anche l'ottimizzazione dei processi, il miglioramento delle prestazioni delle apparecchiature e il controllo preciso dei parametri di dicing. Questi progressi mirano a garantire elevata precisione, efficienza e stabilità nel processo di dicing dei wafer, soddisfacendo l'esigenza dell'industria dei semiconduttori di dimensioni ridotte, maggiore integrazione e strutture dei chip più complesse.

| Area di miglioramento | Misure specifiche | Effetti |

| Ottimizzazione dei processi | - Migliorare i preparativi iniziali, ad esempio un posizionamento più accurato dei wafer e una pianificazione più accurata del percorso. | - Ridurre gli errori di taglio e migliorare la stabilità. |

| - Ridurre al minimo gli errori di taglio e migliorare la stabilità. | - Adottare meccanismi di monitoraggio e feedback in tempo reale per regolare la pressione, la velocità e la temperatura dell'utensile. | |

| - Ridurre i tassi di rottura dei wafer e migliorare la qualità dei chip. | ||

| Miglioramento delle prestazioni delle apparecchiature | - Utilizzare sistemi meccanici ad alta precisione e tecnologie di controllo dell'automazione avanzate. | - Migliora la precisione del taglio e riduce lo spreco di materiale. |

| - Introdurre la tecnologia di taglio laser adatta ai wafer di materiali ad alta durezza. | - Migliorare l'efficienza produttiva e ridurre gli errori manuali. | |

| - Aumentare l'automazione delle apparecchiature per il monitoraggio e le regolazioni automatiche. | ||

| Controllo preciso dei parametri | - Regolare con precisione parametri quali profondità di taglio, velocità, tipo di utensile e metodi di raffreddamento. | - Garantire l'integrità dello stampo e le prestazioni elettriche. |

| - Personalizzare i parametri in base al materiale, allo spessore e alla struttura del wafer. | - Aumentare i tassi di resa, ridurre gli sprechi di materiale e abbassare i costi di produzione. | |

| Significato strategico | - Esplorare continuamente nuovi percorsi tecnologici, ottimizzare i processi e migliorare le capacità delle apparecchiature per soddisfare le richieste del mercato. | - Migliorare la resa e le prestazioni della produzione di chip, supportando lo sviluppo di nuovi materiali e progetti di chip avanzati. |

1.2 L'importanza del taglio a cubetti dei wafer

Il taglio dei wafer svolge un ruolo fondamentale nel processo di produzione dei semiconduttori, influenzando direttamente le fasi successive, nonché la qualità e le prestazioni del prodotto finale. La sua importanza può essere dettagliata come segue:

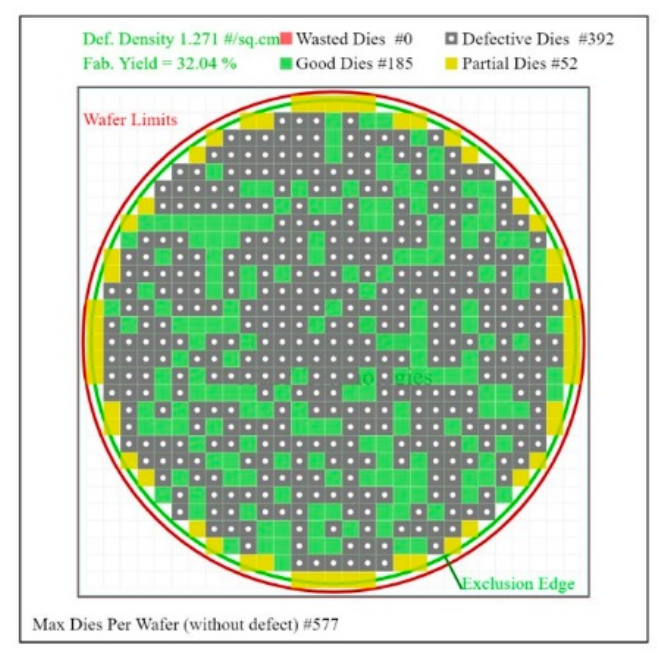

In primo luogo, l'accuratezza e la coerenza del dicing sono fondamentali per garantire la resa e l'affidabilità del chip. Durante la produzione, i wafer vengono sottoposti a molteplici fasi di lavorazione per formare numerose e complesse strutture circuitali, che devono essere suddivise con precisione in singoli chip (die). Se si verificano errori significativi di allineamento o taglio durante il processo di dicing, i circuiti potrebbero danneggiarsi, compromettendo la funzionalità e l'affidabilità del chip. Pertanto, la tecnologia di dicing ad alta precisione non solo garantisce l'integrità di ciascun chip, ma previene anche danni ai circuiti interni, migliorando il tasso di resa complessivo.

In secondo luogo, il taglio a cubetti dei wafer ha un impatto significativo sull'efficienza produttiva e sul controllo dei costi. Essendo una fase cruciale del processo di produzione, la sua efficienza influenza direttamente l'avanzamento delle fasi successive. Ottimizzando il processo di taglio a cubetti, aumentando i livelli di automazione e migliorando la velocità di taglio, è possibile migliorare notevolmente l'efficienza produttiva complessiva.

D'altro canto, lo spreco di materiale durante il taglio a cubetti è un fattore critico nella gestione dei costi. L'utilizzo di tecnologie di taglio avanzate non solo riduce le perdite di materiale non necessarie durante il processo di taglio, ma aumenta anche l'utilizzo dei wafer, riducendo così i costi di produzione.

Con i progressi nella tecnologia dei semiconduttori, i diametri dei wafer continuano ad aumentare e, di conseguenza, la densità dei circuiti, imponendo requisiti più elevati alla tecnologia di dicing. Wafer più grandi richiedono un controllo più preciso dei percorsi di taglio, soprattutto nelle aree ad alta densità di circuiti, dove anche piccole deviazioni possono rendere difettosi più chip. Inoltre, wafer più grandi richiedono più linee di taglio e fasi di processo più complesse, il che richiede ulteriori miglioramenti in termini di precisione, coerenza ed efficienza delle tecnologie di dicing per affrontare queste sfide.

1.3 Processo di taglio dei wafer

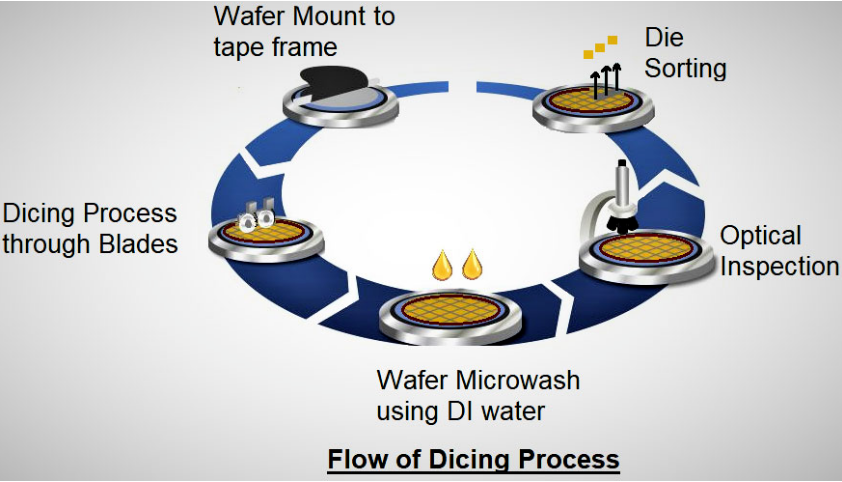

Il processo di taglio dei wafer comprende tutte le fasi, dalla preparazione al controllo qualità finale, e ogni fase è fondamentale per garantire la qualità e le prestazioni dei chip tagliati a cubetti. Di seguito una spiegazione dettagliata di ciascuna fase.

| Fase | Descrizione dettagliata |

| Fase di preparazione | -Pulizia delle cialde: Utilizzare acqua ad alta purezza e detergenti specializzati, combinati con lavaggio meccanico o a ultrasuoni, per rimuovere impurità, particelle e contaminanti, garantendo una superficie pulita. -Posizionamento preciso: Utilizzare attrezzature ad alta precisione per garantire che il wafer venga diviso accuratamente lungo i percorsi di taglio progettati. -Fissaggio del wafer: Fissare il wafer su un telaio di nastro adesivo per mantenerne la stabilità durante il taglio, evitando danni dovuti a vibrazioni o movimenti. |

| Fase di taglio | -Taglio a dadini con lama: Utilizza lame diamantate rotanti ad alta velocità per il taglio fisico, adatte a materiali a base di silicio e convenienti. -Taglio laser a dadi: Utilizza raggi laser ad alta energia per il taglio senza contatto, ideale per materiali fragili o ad alta durezza come il nitruro di gallio, offrendo maggiore precisione e minore perdita di materiale. -Nuove tecnologie: Introdurre tecnologie di taglio laser e al plasma per migliorare ulteriormente l'efficienza e la precisione, riducendo al minimo le zone interessate dal calore. |

| Fase di pulizia | - Utilizzare acqua deionizzata (acqua DI) e detergenti specializzati, combinati con la pulizia a ultrasuoni o a spruzzo, per rimuovere detriti e polvere generati durante il taglio, evitando che i residui influiscano sui processi successivi o sulle prestazioni elettriche del truciolo. - L'acqua deionizzata ad elevata purezza evita l'introduzione di nuovi contaminanti, garantendo un ambiente wafer pulito. |

| Fase di ispezione | -Ispezione ottica: Utilizzare sistemi di rilevamento ottico combinati con algoritmi di intelligenza artificiale per identificare rapidamente i difetti, assicurando che non si formino crepe o scheggiature nei trucioli tagliati, migliorando l'efficienza dell'ispezione e riducendo l'errore umano. -Misurazione delle dimensioni: Verificare che le dimensioni del chip siano conformi alle specifiche di progettazione. -Test delle prestazioni elettriche: Garantire che le prestazioni elettriche dei chip critici siano conformi agli standard, garantendo l'affidabilità nelle applicazioni successive. |

| Fase di smistamento | - Utilizzare bracci robotici o ventose a vuoto per separare i chip qualificati dal telaio del nastro e ordinarli automaticamente in base alle prestazioni, garantendo efficienza e flessibilità della produzione e migliorando al contempo la precisione. |

Il processo di taglio dei wafer prevede la pulizia, il posizionamento, il taglio, la pulizia, l'ispezione e la selezione dei wafer, e ogni fase è fondamentale. Grazie ai progressi nell'automazione, nel taglio laser e nelle tecnologie di ispezione basate sull'intelligenza artificiale, i moderni sistemi di taglio dei wafer possono raggiungere maggiore precisione, velocità e minori perdite di materiale. In futuro, nuove tecnologie di taglio come il laser e il plasma sostituiranno gradualmente il tradizionale taglio a lama per soddisfare le esigenze di progetti di chip sempre più complessi, favorendo ulteriormente lo sviluppo dei processi di produzione dei semiconduttori.

Tecnologia di taglio dei wafer e i suoi principi

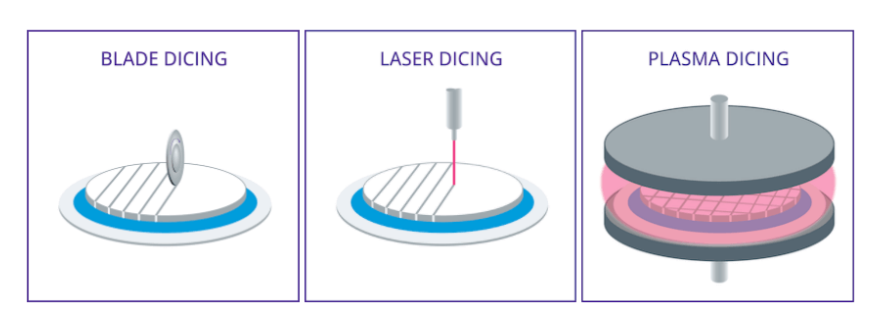

L'immagine illustra tre comuni tecnologie di taglio dei wafer:Taglio a dadini con lama,Taglio laser a dadi, ETaglio al plasmaDi seguito un'analisi dettagliata e una spiegazione supplementare di queste tre tecniche:

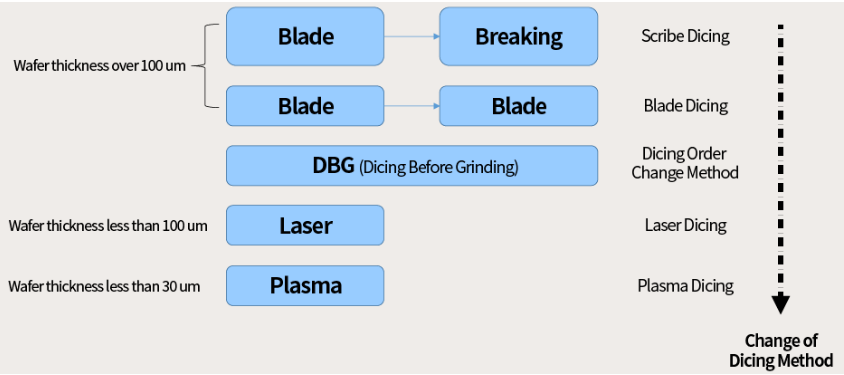

Nella produzione di semiconduttori, il taglio dei wafer è una fase cruciale che richiede la selezione del metodo di taglio appropriato in base allo spessore del wafer. Il primo passo è determinare lo spessore del wafer. Se lo spessore del wafer supera i 100 micron, si può scegliere il metodo di taglio a lama. Se il metodo di taglio a lama non è adatto, si può utilizzare il metodo di taglio a frattura, che include sia la tecnica di taglio a incisione che quella a lama.

Quando lo spessore del wafer è compreso tra 30 e 100 micron, si consiglia il metodo DBG (Dice Before Grinding). In questo caso, per ottenere risultati ottimali, è possibile scegliere tra il taglio a incisione, il taglio a lama o la regolazione della sequenza di taglio secondo necessità.

Per wafer ultrasottili con spessore inferiore a 30 micron, il taglio laser diventa il metodo preferito grazie alla sua capacità di tagliare i wafer sottili con precisione senza causare danni eccessivi. Se il taglio laser non può soddisfare requisiti specifici, è possibile utilizzare il taglio al plasma come alternativa. Questo diagramma di flusso fornisce un chiaro percorso decisionale per garantire la scelta della tecnologia di taglio dei wafer più adatta in diverse condizioni di spessore.

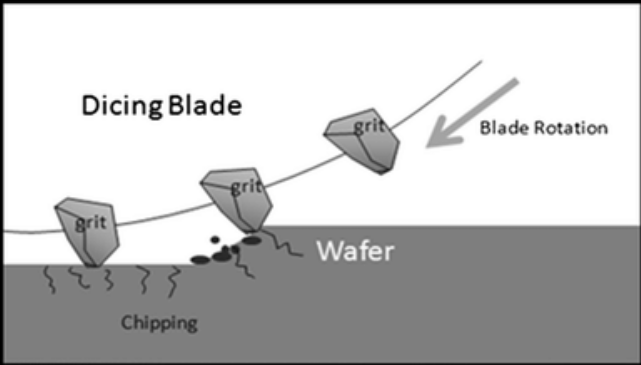

2.1 Tecnologia di taglio meccanico

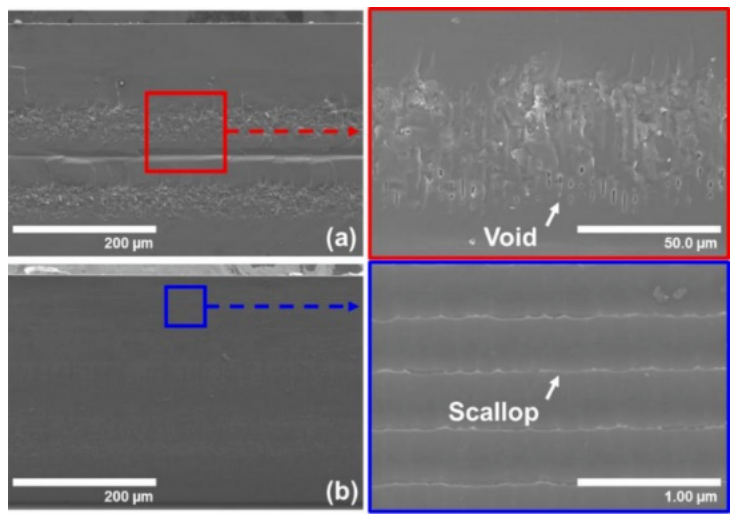

La tecnologia di taglio meccanico è il metodo tradizionale per il taglio a cubetti dei wafer. Il principio fondamentale è l'utilizzo di una mola diamantata rotante ad alta velocità come utensile da taglio per tagliare il wafer. L'attrezzatura principale include un mandrino con cuscinetto ad aria, che aziona la mola diamantata ad alta velocità per eseguire tagli o scanalature precisi lungo un percorso di taglio predefinito. Questa tecnologia è ampiamente utilizzata nel settore grazie al suo basso costo, all'elevata efficienza e all'ampia applicabilità.

Vantaggi

L'elevata durezza e resistenza all'usura degli utensili con mole diamantate consente alla tecnologia di taglio meccanico di adattarsi alle esigenze di taglio di vari materiali per wafer, dai tradizionali materiali a base di silicio ai più recenti semiconduttori composti. Il suo funzionamento è semplice, con requisiti tecnici relativamente bassi, il che ne promuove ulteriormente la popolarità nella produzione di massa. Inoltre, rispetto ad altri metodi di taglio come il taglio laser, il taglio meccanico presenta costi più controllabili, rendendolo adatto alle esigenze di produzione di grandi volumi.

Limitazioni

Nonostante i suoi numerosi vantaggi, la tecnologia di taglio meccanico presenta anche dei limiti. In primo luogo, a causa del contatto fisico tra l'utensile e il wafer, la precisione di taglio è relativamente limitata, causando spesso deviazioni dimensionali che possono influire sulla precisione del successivo confezionamento e collaudo del chip. In secondo luogo, durante il processo di taglio meccanico possono verificarsi facilmente difetti come scheggiature e crepe, che non solo influiscono sul tasso di resa, ma possono anche avere un impatto negativo sull'affidabilità e sulla durata dei chip. I danni indotti dalle sollecitazioni meccaniche sono particolarmente dannosi per la produzione di chip ad alta densità, soprattutto quando si tagliano materiali fragili, dove questi problemi sono più evidenti.

Miglioramenti tecnologici

Per superare queste limitazioni, i ricercatori stanno ottimizzando costantemente il processo di taglio meccanico. Tra i principali miglioramenti figurano il miglioramento della progettazione e della selezione dei materiali delle mole per aumentare la precisione e la durata del taglio. Inoltre, l'ottimizzazione della progettazione strutturale e dei sistemi di controllo delle attrezzature di taglio ha ulteriormente migliorato la stabilità e l'automazione del processo. Questi progressi riducono gli errori causati dalle operazioni umane e migliorano l'uniformità dei tagli. L'introduzione di tecnologie avanzate di ispezione e controllo qualità per il monitoraggio in tempo reale delle anomalie durante il processo di taglio ha inoltre migliorato significativamente l'affidabilità e la resa del taglio.

Sviluppo futuro e nuove tecnologie

Sebbene la tecnologia di taglio meccanico ricopra ancora un ruolo significativo nel taglio dei wafer, nuove tecnologie di taglio stanno rapidamente avanzando con l'evoluzione dei processi dei semiconduttori. Ad esempio, l'applicazione della tecnologia di taglio laser termico offre nuove soluzioni ai problemi di precisione e di difettosità nel taglio meccanico. Questo metodo di taglio senza contatto riduce lo stress fisico sul wafer, riducendo significativamente l'incidenza di scheggiature e cricche, soprattutto durante il taglio di materiali più fragili. In futuro, l'integrazione della tecnologia di taglio meccanico con le tecniche di taglio emergenti offrirà alla produzione di semiconduttori maggiori opzioni e flessibilità, migliorando ulteriormente l'efficienza produttiva e la qualità dei chip.

In conclusione, nonostante la tecnologia del taglio meccanico presenti alcuni svantaggi, i continui miglioramenti tecnologici e la sua integrazione con nuove tecniche di taglio le consentono di continuare a svolgere un ruolo importante nella produzione di semiconduttori e di mantenere la sua competitività nei processi futuri.

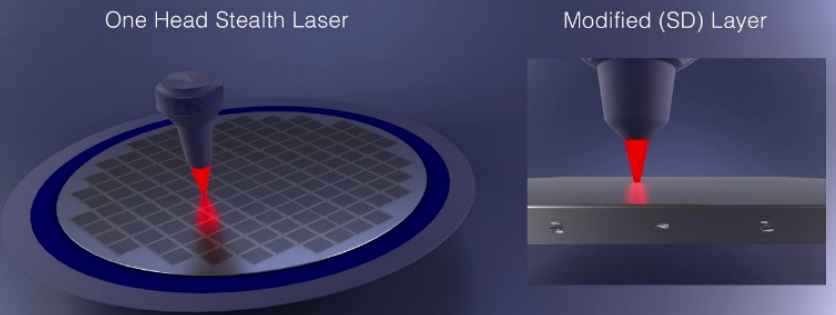

2.2 Tecnologia di taglio laser

La tecnologia di taglio laser, come nuovo metodo di taglio dei wafer, ha gradualmente guadagnato ampia attenzione nel settore dei semiconduttori grazie alla sua elevata precisione, all'assenza di danni da contatto meccanico e alla rapidità di taglio. Questa tecnologia sfrutta l'elevata densità energetica e la capacità di focalizzazione di un raggio laser per creare una piccola zona termicamente alterata sulla superficie del materiale del wafer. Quando il raggio laser viene applicato al wafer, lo stress termico generato provoca la frattura del materiale nel punto designato, ottenendo un taglio preciso.

Vantaggi della tecnologia di taglio laser

• Alta precisione: La precisa capacità di posizionamento del raggio laser consente una precisione di taglio a livello di micron o addirittura nanometri, soddisfacendo i requisiti della moderna produzione di circuiti integrati ad alta precisione e ad alta densità.

• Nessun contatto meccanico: Il taglio laser evita il contatto fisico con il wafer, prevenendo i problemi comuni del taglio meccanico, come scheggiature e crepe, migliorando significativamente il tasso di resa e l'affidabilità dei chip.

• Velocità di taglio elevata: L'elevata velocità del taglio laser contribuisce ad aumentare l'efficienza produttiva, rendendolo particolarmente adatto a scenari di produzione su larga scala e ad alta velocità.

Sfide affrontate

• Elevato costo delle attrezzature: L'investimento iniziale per le attrezzature di taglio laser è elevato, il che comporta una pressione economica, soprattutto per le piccole e medie imprese di produzione.

• Controllo di processo complesso:Il taglio laser richiede un controllo preciso di diversi parametri, tra cui la densità energetica, la posizione di messa a fuoco e la velocità di taglio, rendendo il processo complesso.

• Problemi nelle zone colpite dal calore: Sebbene la natura senza contatto del taglio laser riduca i danni meccanici, lo stress termico causato dalla zona termicamente alterata (ZTA) può influire negativamente sulle proprietà del materiale del wafer. È necessaria un'ulteriore ottimizzazione del processo per ridurre al minimo questo effetto.

Direzioni di miglioramento tecnologico

Per affrontare queste sfide, i ricercatori si stanno concentrando sulla riduzione dei costi delle attrezzature, sul miglioramento dell'efficienza di taglio e sull'ottimizzazione del flusso del processo.

• Laser e sistemi ottici efficienti: Sviluppando laser più efficienti e sistemi ottici avanzati, è possibile ridurre i costi delle attrezzature, migliorando al contempo la precisione e la velocità di taglio.

• Ottimizzazione dei parametri di processo:Sono in corso ricerche approfondite sull'interazione tra laser e materiali per wafer per migliorare i processi che riducono la zona termicamente alterata, migliorando così la qualità del taglio.

• Sistemi di controllo intelligenti: Lo sviluppo di tecnologie di controllo intelligenti mira ad automatizzare e ottimizzare il processo di taglio laser, migliorandone la stabilità e la coerenza.

La tecnologia di taglio laser è particolarmente efficace nei wafer ultrasottili e negli scenari di taglio ad alta precisione. Con l'aumento delle dimensioni dei wafer e della densità dei circuiti, i tradizionali metodi di taglio meccanico faticano a soddisfare i requisiti di alta precisione ed efficienza della moderna produzione di semiconduttori. Grazie ai suoi vantaggi unici, il taglio laser sta diventando la soluzione preferita in questi settori.

Sebbene la tecnologia del taglio laser debba ancora affrontare sfide quali gli elevati costi delle attrezzature e la complessità del processo, i suoi vantaggi unici in termini di elevata precisione e danneggiamento senza contatto la rendono un'importante direzione di sviluppo nella produzione di semiconduttori. Con il continuo progresso della tecnologia laser e dei sistemi di controllo intelligenti, si prevede che il taglio laser migliorerà ulteriormente l'efficienza e la qualità del taglio dei wafer, guidando il continuo sviluppo dell'industria dei semiconduttori.

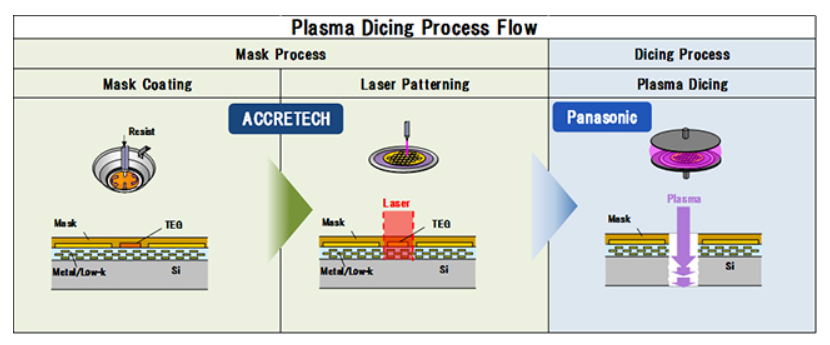

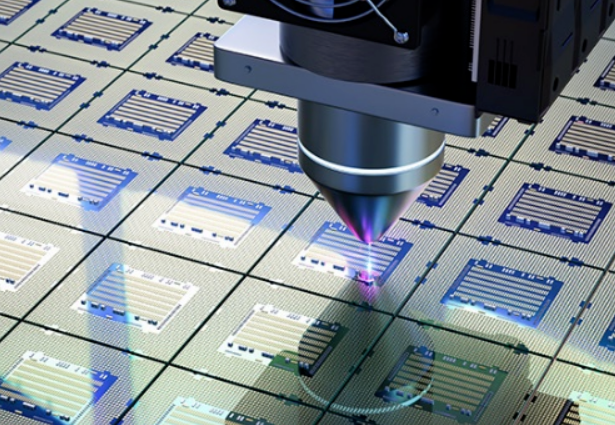

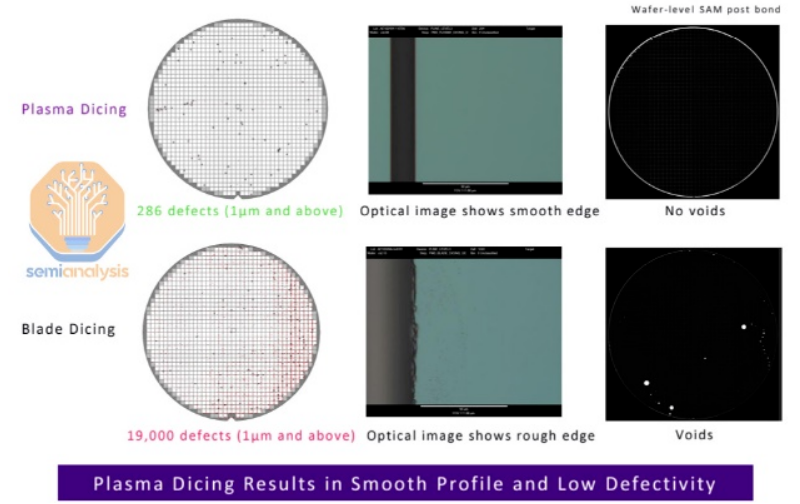

2.3 Tecnologia di taglio al plasma

La tecnologia di taglio al plasma, come metodo emergente per il taglio a cubetti dei wafer, ha ricevuto notevole attenzione negli ultimi anni. Questa tecnologia utilizza fasci di plasma ad alta energia per tagliare con precisione i wafer, controllando l'energia, la velocità e il percorso di taglio del fascio di plasma, ottenendo risultati di taglio ottimali.

Principio di funzionamento e vantaggi

Il processo di taglio al plasma si basa su un fascio di plasma ad alta temperatura e alta energia generato dall'apparecchiatura. Questo fascio può riscaldare il materiale del wafer fino al suo punto di fusione o vaporizzazione in un tempo molto breve, consentendo un taglio rapido. Rispetto al taglio meccanico o laser tradizionale, il taglio al plasma è più veloce e produce una zona termicamente alterata più piccola, riducendo efficacemente la formazione di crepe e danni durante il taglio.

Nelle applicazioni pratiche, la tecnologia di taglio al plasma è particolarmente indicata per la lavorazione di wafer di forme complesse. Il suo fascio di plasma ad alta energia e regolabile può tagliare facilmente wafer di forma irregolare con elevata precisione. Pertanto, nella produzione microelettronica, in particolare nella produzione personalizzata e in piccoli lotti di chip di fascia alta, questa tecnologia si dimostra molto promettente per un utilizzo su larga scala.

Sfide e limitazioni

Nonostante i numerosi vantaggi, la tecnologia del taglio al plasma presenta anche alcune sfide.

• Processo complesso: Il processo di taglio al plasma è complesso e richiede attrezzature ad alta precisione e operatori esperti per garantireprecisione e stabilità nel taglio.

• Controllo ambientale e sicurezza: La natura ad alta temperatura e ad alta energia del fascio di plasma richiede rigorosi controlli ambientali e misure di sicurezza, il che aumenta la complessità e i costi di implementazione.

Direzioni di sviluppo futuro

Con i progressi tecnologici, si prevede che le sfide associate al taglio al plasma saranno gradualmente superate. Sviluppando apparecchiature di taglio più intelligenti e stabili, è possibile ridurre la dipendenza dalle operazioni manuali, migliorando così l'efficienza produttiva. Allo stesso tempo, l'ottimizzazione dei parametri di processo e dell'ambiente di taglio contribuirà a ridurre i rischi per la sicurezza e i costi operativi.

Nell'industria dei semiconduttori, le innovazioni nelle tecnologie di taglio e taglio dei wafer sono cruciali per guidare lo sviluppo del settore. La tecnologia di taglio al plasma, con la sua elevata precisione, efficienza e capacità di gestire wafer di forme complesse, si è affermata come un nuovo attore significativo in questo campo. Sebbene permangano alcune sfide, queste saranno gradualmente affrontate con la continua innovazione tecnologica, offrendo maggiori possibilità e opportunità alla produzione di semiconduttori.

Le prospettive applicative della tecnologia del taglio al plasma sono vaste e si prevede che in futuro svolgerà un ruolo sempre più importante nella produzione di semiconduttori. Grazie alla continua innovazione e ottimizzazione tecnologica, il taglio al plasma non solo risolverà le sfide attuali, ma diventerà anche un potente motore di crescita per l'industria dei semiconduttori.

2.4 Qualità del taglio e fattori che influenzano

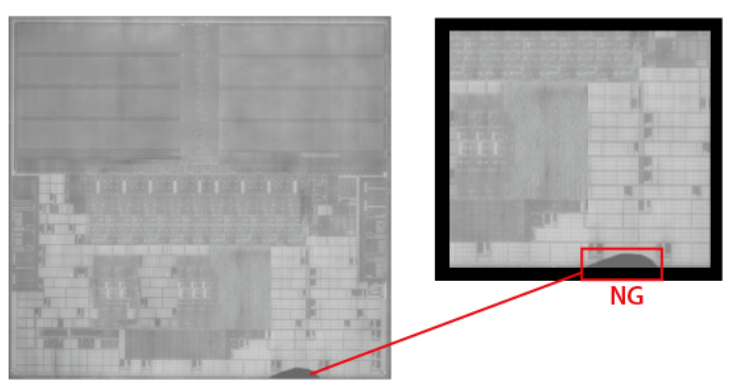

La qualità del taglio dei wafer è fondamentale per il successivo confezionamento dei chip, i test e le prestazioni e l'affidabilità complessive del prodotto finale. Tra i problemi più comuni riscontrati durante il taglio figurano crepe, scheggiature e deviazioni di taglio. Questi problemi sono influenzati da diversi fattori concomitanti.

| Categoria | Contenuto | Impatto |

| Parametri di processo | Velocità di taglio, avanzamento e profondità di taglio influiscono direttamente sulla stabilità e sulla precisione del processo di taglio. Impostazioni errate possono portare a una concentrazione di sollecitazioni e a un'eccessiva zona termicamente alterata, con conseguenti cricche e scheggiature. Regolare i parametri in modo appropriato in base al materiale del wafer, allo spessore e alle esigenze di taglio è fondamentale per ottenere i risultati di taglio desiderati. | I giusti parametri di processo garantiscono un taglio preciso e riducono il rischio di difetti come crepe e scheggiature. |

| Fattori relativi alle attrezzature e ai materiali | -Qualità della lama: Il materiale, la durezza e la resistenza all'usura della lama influenzano la scorrevolezza del processo di taglio e la planarità della superficie di taglio. Lame di scarsa qualità aumentano l'attrito e lo stress termico, causando potenzialmente crepe o scheggiature. La scelta del materiale giusto per la lama è fondamentale. -Prestazioni del refrigerante: I refrigeranti aiutano a ridurre la temperatura di taglio, a ridurre al minimo l'attrito e a rimuovere i detriti. Un refrigerante inefficace può portare a temperature elevate e all'accumulo di detriti, influendo sulla qualità e sull'efficienza del taglio. Scegliere refrigeranti efficienti ed ecocompatibili è fondamentale. | La qualità della lama influisce sulla precisione e sulla scorrevolezza del taglio. Un refrigerante inefficace può compromettere la qualità e l'efficienza del taglio, evidenziando la necessità di un utilizzo ottimale del refrigerante. |

| Controllo di processo e ispezione di qualità | -Controllo di processo: Monitoraggio e regolazione in tempo reale dei parametri di taglio chiave per garantire stabilità e coerenza nel processo di taglio. -Controllo di qualità: I controlli dell'aspetto post-taglio, le misurazioni dimensionali e i test delle prestazioni elettriche aiutano a identificare e risolvere tempestivamente i problemi di qualità, migliorando la precisione e la coerenza del taglio. | Un adeguato controllo del processo e un'ispezione di qualità contribuiscono a garantire risultati di taglio costanti e di alta qualità e a individuare tempestivamente potenziali problemi. |

Miglioramento della qualità del taglio

Il miglioramento della qualità del taglio richiede un approccio globale che tenga conto dei parametri di processo, della selezione delle attrezzature e dei materiali, del controllo di processo e dell'ispezione. Grazie al continuo perfezionamento delle tecnologie di taglio e all'ottimizzazione dei metodi di processo, è possibile migliorare ulteriormente la precisione e la stabilità del taglio dei wafer, fornendo un supporto tecnico più affidabile per l'industria manifatturiera dei semiconduttori.

#03 Gestione e test post-taglio

3.1 Pulizia e asciugatura

Le fasi di pulizia e asciugatura dopo il taglio dei wafer sono fondamentali per garantire la qualità dei chip e il corretto svolgimento dei processi successivi. Durante questa fase, è essenziale rimuovere accuratamente detriti di silicio, residui di refrigerante e altri contaminanti generati durante il taglio. È altrettanto importante assicurarsi che i chip non vengano danneggiati durante il processo di pulizia e, dopo l'asciugatura, assicurarsi che non rimanga umidità sulla superficie del chip per prevenire problemi come corrosione o scariche elettrostatiche.

Gestione post-taglio: processo di pulizia e asciugatura

| Fase del processo | Contenuto | Impatto |

| Processo di pulizia | -Metodo: Per la pulizia utilizzare detergenti specializzati e acqua pura, abbinati a tecniche di spazzolatura meccanica o a ultrasuoni. | Assicura la rimozione completa dei contaminanti e previene danni ai trucioli durante la pulizia. |

| -Selezione dell'agente detergente: Scegliere in base al materiale del wafer e al tipo di contaminante per garantire una pulizia efficace senza danneggiare il chip. | La scelta corretta dell'agente è fondamentale per una pulizia efficace e una protezione dai trucioli. | |

| -Controllo dei parametri: Controllare rigorosamente la temperatura, il tempo e la concentrazione della soluzione detergente per prevenire problemi di qualità causati da una pulizia impropria. | I controlli aiutano a evitare di danneggiare il wafer o di lasciare contaminanti, garantendo una qualità costante. | |

| Processo di essiccazione | -Metodi tradizionali: Essiccazione ad aria naturale e ad aria calda, che hanno una bassa efficienza e possono causare accumulo di elettricità statica. | Potrebbe rallentare i tempi di asciugatura e causare potenziali problemi di elettricità statica. |

| -Tecnologie moderne: Utilizzare tecnologie avanzate come l'essiccazione sotto vuoto e l'essiccazione a infrarossi per garantire che i trucioli si asciughino rapidamente ed evitare effetti dannosi. | Processo di asciugatura più rapido ed efficiente, riducendo il rischio di scariche elettrostatiche o problemi legati all'umidità. | |

| Selezione e manutenzione delle attrezzature | -Selezione dell'attrezzatura: Le macchine per la pulizia e l'asciugatura ad alte prestazioni migliorano l'efficienza della lavorazione e controllano con precisione i potenziali problemi durante la movimentazione. | Macchine di alta qualità garantiscono una migliore lavorazione e riducono la probabilità di errori durante la pulizia e l'asciugatura. |

| -Manutenzione delle attrezzature: L'ispezione e la manutenzione regolari delle apparecchiature garantiscono che rimangano in condizioni di funzionamento ottimali, garantendo la qualità dei trucioli. | Una corretta manutenzione previene i guasti delle apparecchiature, garantendo un'elaborazione affidabile e di alta qualità. |

Pulizia e asciugatura post-taglio

Le fasi di pulizia e asciugatura dopo il taglio dei wafer sono processi complessi e delicati che richiedono un'attenta valutazione di molteplici fattori per garantire il risultato finale della lavorazione. Utilizzando metodi scientifici e procedure rigorose, è possibile garantire che ogni chip arrivi alle successive fasi di confezionamento e collaudo in condizioni ottimali.

Ispezione e collaudo post-taglio

| Fare un passo | Contenuto | Impatto |

| Fase di ispezione | 1.Ispezione visiva: Utilizzare apparecchiature di ispezione visiva o automatizzata per verificare la presenza di difetti visibili come crepe, scheggiature o contaminazione sulla superficie del truciolo. Identificare rapidamente i trucioli danneggiati fisicamente per evitare sprechi. | Aiuta a identificare ed eliminare i trucioli difettosi nelle prime fasi del processo, riducendo la perdita di materiale. |

| 2.Misurazione delle dimensioni: Utilizzare dispositivi di misurazione di precisione per misurare con precisione le dimensioni dei chip, assicurando che le dimensioni del taglio soddisfino le specifiche di progettazione ed evitando problemi di prestazioni o difficoltà di confezionamento. | Garantisce che i chip rientrino nei limiti dimensionali richiesti, prevenendo il degrado delle prestazioni o problemi di assemblaggio. | |

| 3.Test delle prestazioni elettriche: Valutare i parametri elettrici chiave, quali resistenza, capacità e induttanza, per identificare i chip non conformi e garantire che solo i chip qualificati in termini di prestazioni passino alla fase successiva. | Garantisce che solo i chip funzionali e con prestazioni testate vengano avviati nel processo, riducendo il rischio di guasti nelle fasi successive. | |

| Fase di test | 1.Test funzionali: Verificare che le funzionalità di base del chip funzionino come previsto, identificando ed eliminando i chip con anomalie funzionali. | Assicura che i chip soddisfino i requisiti operativi di base prima di passare alle fasi successive. |

| 2.Test di affidabilità: Valutare la stabilità delle prestazioni del chip in condizioni di utilizzo prolungato o in ambienti difficili, in genere mediante invecchiamento ad alta temperatura, test a bassa temperatura e test di umidità per simulare condizioni estreme del mondo reale. | Garantisce che i chip possano funzionare in modo affidabile in una vasta gamma di condizioni ambientali, migliorando la longevità e la stabilità del prodotto. | |

| 3.Test di compatibilità: Verificare che il chip funzioni correttamente con altri componenti o sistemi, assicurandosi che non vi siano guasti o degrado delle prestazioni dovuti a incompatibilità. | Garantisce un funzionamento fluido nelle applicazioni reali prevenendo problemi di compatibilità. |

3.3 Imballaggio e stoccaggio

Dopo il taglio dei wafer, i chip rappresentano un prodotto fondamentale del processo di produzione dei semiconduttori, e le fasi di confezionamento e stoccaggio sono altrettanto importanti. Misure di confezionamento e stoccaggio adeguate sono essenziali non solo per garantire la sicurezza e la stabilità dei chip durante il trasporto e lo stoccaggio, ma anche per fornire un solido supporto alle successive fasi di produzione, collaudo e confezionamento.

Riepilogo delle fasi di ispezione e collaudo:

Le fasi di ispezione e collaudo dei chip dopo il taglio dei wafer coprono una vasta gamma di aspetti, tra cui ispezione visiva, misurazione delle dimensioni, test delle prestazioni elettriche, test funzionali, test di affidabilità e test di compatibilità. Queste fasi sono interconnesse e complementari, costituendo una solida barriera per garantire la qualità e l'affidabilità del prodotto. Attraverso rigorose procedure di ispezione e collaudo, è possibile identificare e risolvere tempestivamente potenziali problemi, garantendo che il prodotto finale soddisfi i requisiti e le aspettative del cliente.

| Aspetto | Contenuto |

| Misure di imballaggio | 1.Antistatico: I materiali di imballaggio devono avere eccellenti proprietà antistatiche per impedire che l'elettricità statica danneggi i dispositivi o ne comprometta le prestazioni. |

| 2.A prova di umidità: I materiali di imballaggio devono avere una buona resistenza all'umidità per prevenire la corrosione e il deterioramento delle prestazioni elettriche causato dall'umidità. | |

| 3.Antiurto: I materiali di imballaggio devono garantire un efficace assorbimento degli urti per proteggere i trucioli dalle vibrazioni e dagli urti durante il trasporto. | |

| Ambiente di archiviazione | 1.Controllo dell'umidità: Controllare rigorosamente l'umidità entro un intervallo appropriato per prevenire l'assorbimento di umidità e la corrosione causati da umidità eccessiva o problemi di elettricità statica causati da bassa umidità. |

| 2.Pulizia: Mantenere un ambiente di stoccaggio pulito per evitare la contaminazione dei trucioli da parte di polvere e impurità. | |

| 3.Controllo della temperatura: Impostare un intervallo di temperatura ragionevole e mantenere la stabilità della temperatura per prevenire l'invecchiamento accelerato dovuto a calore eccessivo o problemi di condensa causati da basse temperature. | |

| Ispezione regolare | Ispezionare e valutare regolarmente i trucioli immagazzinati, utilizzando ispezioni visive, misurazioni dimensionali e test delle prestazioni elettriche per identificare e risolvere tempestivamente potenziali problemi. In base al tempo e alle condizioni di stoccaggio, pianificare l'utilizzo dei trucioli per garantire che vengano utilizzati in condizioni ottimali. |

Il problema delle microfratture e dei danni durante il processo di taglio dei wafer rappresenta una sfida significativa nella produzione di semiconduttori. Lo stress da taglio è la causa principale di questo fenomeno, poiché crea minuscole crepe e danni sulla superficie del wafer, con conseguente aumento dei costi di produzione e una riduzione della qualità del prodotto.

Per affrontare questa sfida, è fondamentale ridurre al minimo lo stress da taglio e implementare tecniche, utensili e condizioni di taglio ottimizzate. Un'attenta valutazione di fattori quali il materiale della lama, la velocità di taglio, la pressione e i metodi di raffreddamento può contribuire a ridurre la formazione di microfratture e migliorare la resa complessiva del processo. Inoltre, la ricerca in corso su tecnologie di taglio più avanzate, come il taglio laser, sta esplorando modi per mitigare ulteriormente questi problemi.

Essendo un materiale fragile, i wafer sono soggetti a cambiamenti strutturali interni quando sottoposti a stress meccanici, termici o chimici, che portano alla formazione di microfratture. Sebbene queste crepe possano non essere immediatamente visibili, possono espandersi e causare danni più gravi con il progredire del processo di produzione. Questo problema diventa particolarmente problematico durante le successive fasi di confezionamento e collaudo, dove le fluttuazioni di temperatura e ulteriori stress meccanici possono far sì che queste microfratture si trasformino in fratture visibili, con conseguente potenziale rottura del chip.

Per mitigare questo rischio, è essenziale controllare attentamente il processo di taglio ottimizzando parametri quali velocità, pressione e temperatura. L'utilizzo di metodi di taglio meno aggressivi, come il laser dicing, può ridurre lo stress meccanico sul wafer e minimizzare la formazione di microfratture. Inoltre, l'implementazione di metodi di ispezione avanzati come la scansione a infrarossi o l'imaging a raggi X durante il processo di taglio del wafer può aiutare a rilevare queste cricche in fase iniziale prima che causino ulteriori danni.

Il danneggiamento della superficie del wafer è un problema significativo nel processo di taglio, in quanto può avere un impatto diretto sulle prestazioni e sull'affidabilità del chip. Tali danni possono essere causati da un uso improprio degli utensili da taglio, da parametri di taglio errati o da difetti dei materiali intrinseci del wafer stesso. Indipendentemente dalla causa, questi danni possono portare ad alterazioni della resistenza elettrica o della capacità del circuito, compromettendo le prestazioni complessive.

Per affrontare queste problematiche, si stanno esplorando due strategie chiave:

1. Ottimizzazione degli utensili e dei parametri di taglio: Utilizzando lame più affilate, regolando la velocità di taglio e modificando la profondità di taglio, è possibile ridurre al minimo la concentrazione di stress durante il processo di taglio, riducendo così il rischio di danni.

2. Esplorare nuove tecnologie di taglio: Tecniche avanzate come il taglio laser e il taglio al plasma offrono una maggiore precisione, riducendo potenzialmente il livello di danno inflitto al wafer. Queste tecnologie sono allo studio per trovare modi per ottenere un'elevata precisione di taglio riducendo al minimo lo stress termico e meccanico sul wafer.

Area di impatto termico e suoi effetti sulle prestazioni

Nei processi di taglio termico come il taglio laser e al plasma, le alte temperature creano inevitabilmente una zona di impatto termico sulla superficie del wafer. Quest'area, dove il gradiente di temperatura è significativo, può alterare le proprietà del materiale, influenzando le prestazioni finali del chip.

Impatto della zona termicamente alterata (TAZ):

Cambiamenti nella struttura cristallina: Ad alte temperature, gli atomi all'interno del materiale del wafer possono riorganizzarsi, causando distorsioni nella struttura cristallina. Questa distorsione indebolisce il materiale, riducendone la resistenza meccanica e la stabilità, aumentando il rischio di guasti del chip durante l'uso.

Cambiamenti nelle proprietà elettriche: Le alte temperature possono alterare la concentrazione e la mobilità dei portatori nei materiali semiconduttori, influenzando la conduttività elettrica del chip e l'efficienza di trasmissione della corrente. Queste variazioni possono portare a un calo delle prestazioni del chip, rendendolo potenzialmente inadatto allo scopo previsto.

Per attenuare questi effetti, il controllo della temperatura durante il taglio, l'ottimizzazione dei parametri di taglio e l'esplorazione di metodi come getti di raffreddamento o trattamenti di post-elaborazione sono strategie essenziali per ridurre l'entità dell'impatto termico e mantenere l'integrità del materiale.

Nel complesso, sia le microfratture che le zone di impatto termico rappresentano sfide cruciali nella tecnologia di taglio dei wafer. Saranno necessarie una ricerca continua, unitamente a progressi tecnologici e misure di controllo qualità, per migliorare la qualità dei prodotti semiconduttori e accrescerne la competitività sul mercato.

Misure per il controllo della zona di impatto termico:

Ottimizzazione dei parametri del processo di taglio: Ridurre la velocità e la potenza di taglio può ridurre efficacemente le dimensioni della zona di impatto termico (TAZ). Ciò aiuta a controllare la quantità di calore generato durante il processo di taglio, che ha un impatto diretto sulle proprietà del materiale del wafer.

Tecnologie di raffreddamento avanzate: L'applicazione di tecnologie come il raffreddamento ad azoto liquido e il raffreddamento microfluidico può limitare significativamente l'intervallo della zona di impatto termico. Questi metodi di raffreddamento aiutano a dissipare il calore in modo più efficiente, preservando così le proprietà del materiale del wafer e riducendo al minimo i danni termici.

Selezione dei materiali: I ricercatori stanno esplorando nuovi materiali, come i nanotubi di carbonio e il grafene, che possiedono un'eccellente conduttività termica e resistenza meccanica. Questi materiali possono ridurre la zona di impatto termico migliorando al contempo le prestazioni complessive dei chip.

In sintesi, sebbene la zona di impatto termico sia una conseguenza inevitabile delle tecnologie di taglio termico, può essere efficacemente controllata attraverso tecniche di lavorazione ottimizzate e una selezione accurata dei materiali. La ricerca futura si concentrerà probabilmente sulla messa a punto e sull'automazione dei processi di taglio termico per ottenere un taglio dei wafer più efficiente e preciso.

Strategia di equilibrio:

Raggiungere l'equilibrio ottimale tra resa dei wafer ed efficienza produttiva è una sfida continua nella tecnologia di taglio dei wafer. I produttori devono considerare molteplici fattori, come la domanda del mercato, i costi di produzione e la qualità del prodotto, per sviluppare una strategia di produzione razionale e parametri di processo. Allo stesso tempo, l'introduzione di attrezzature di taglio avanzate, il miglioramento delle competenze degli operatori e il potenziamento del controllo di qualità delle materie prime sono essenziali per mantenere o addirittura migliorare la resa, aumentando al contempo l'efficienza produttiva.

Sfide e opportunità future:

Con il progresso della tecnologia dei semiconduttori, il taglio dei wafer si trova ad affrontare nuove sfide e opportunità. Con la riduzione delle dimensioni dei chip e l'aumento dell'integrazione, le esigenze di precisione e qualità del taglio aumentano in modo significativo. Allo stesso tempo, le tecnologie emergenti forniscono nuove idee per lo sviluppo di tecniche di taglio dei wafer. I produttori devono rimanere al passo con le dinamiche di mercato e le tendenze tecnologiche, adattando e ottimizzando costantemente le strategie di produzione e i parametri di processo per soddisfare i cambiamenti del mercato e le esigenze tecnologiche.

In conclusione, integrando considerazioni sulla domanda del mercato, sui costi di produzione e sulla qualità del prodotto, e introducendo attrezzature e tecnologie avanzate, migliorando le competenze degli operatori e rafforzando il controllo delle materie prime, i produttori possono raggiungere il miglior equilibrio tra resa dei wafer ed efficienza produttiva durante la loro suddivisione, ottenendo così una produzione di prodotti semiconduttori efficiente e di alta qualità.

Prospettive future:

Grazie ai rapidi progressi tecnologici, la tecnologia dei semiconduttori sta progredendo a un ritmo senza precedenti. Come fase fondamentale nella produzione di semiconduttori, la tecnologia di taglio dei wafer è pronta a nuovi entusiasmanti sviluppi. Guardando al futuro, si prevede che la tecnologia di taglio dei wafer raggiungerà significativi miglioramenti in termini di precisione, efficienza e costi, infondendo nuova vitalità alla continua crescita dell'industria dei semiconduttori.

Precisione crescente:

Alla ricerca di una maggiore precisione, la tecnologia di taglio dei wafer continuerà a spingere i limiti dei processi esistenti. Studiando approfonditamente i meccanismi fisici e chimici del processo di taglio e controllando con precisione i parametri di taglio, si otterranno risultati di taglio più precisi, in grado di soddisfare requisiti di progettazione di circuiti sempre più complessi. Inoltre, l'esplorazione di nuovi materiali e metodi di taglio migliorerà significativamente resa e qualità.

Migliorare l'efficienza:

Le nuove apparecchiature per il taglio di wafer si concentreranno su una progettazione intelligente e automatizzata. L'introduzione di sistemi di controllo e algoritmi avanzati consentirà alle apparecchiature di regolare automaticamente i parametri di taglio per adattarsi a diversi materiali e requisiti di progettazione, migliorando così significativamente l'efficienza produttiva. Innovazioni come la tecnologia di taglio multi-wafer e i sistemi di sostituzione rapida delle lame svolgeranno un ruolo cruciale nel migliorare l'efficienza.

Riduzione dei costi:

La riduzione dei costi è un aspetto fondamentale per lo sviluppo della tecnologia di taglio dei wafer. Con lo sviluppo di nuovi materiali e metodi di taglio, si prevede che i costi delle attrezzature e le spese di manutenzione saranno efficacemente controllati. Inoltre, l'ottimizzazione dei processi produttivi e la riduzione degli scarti ridurranno ulteriormente gli sprechi durante la produzione, con conseguente riduzione dei costi di produzione complessivi.

Produzione intelligente e IoT:

L'integrazione tra tecnologie di produzione intelligente e Internet of Things (IoT) porterà cambiamenti radicali nella tecnologia di taglio dei wafer. Grazie all'interconnettività e alla condivisione dei dati tra i dispositivi, ogni fase del processo produttivo può essere monitorata e ottimizzata in tempo reale. Questo non solo migliora l'efficienza produttiva e la qualità del prodotto, ma fornisce anche alle aziende previsioni di mercato più accurate e supporto decisionale.

In futuro, la tecnologia di taglio dei wafer farà notevoli progressi in termini di precisione, efficienza e costi. Questi progressi guideranno il continuo sviluppo dell'industria dei semiconduttori e apporteranno ulteriori innovazioni tecnologiche e vantaggi alla società umana.

Data di pubblicazione: 19-11-2024