Riassunto del wafer di SiC

Wafer di carburo di silicio (SiC)sono diventati il substrato di scelta per l'elettronica ad alta potenza, alta frequenza e alta temperatura nei settori automobilistico, delle energie rinnovabili e aerospaziale. Il nostro portafoglio comprende politipi e schemi di drogaggio chiave: 4H drogato con azoto (4H-N), semiisolante ad alta purezza (HPSI), 3C drogato con azoto (3C-N) e 4H/6H di tipo p (4H/6H-P), offerti in tre livelli di qualità: PRIME (substrati completamente lucidati, di qualità per dispositivi), DUMMY (lappati o non lucidati per prove di processo) e RESEARCH (strati epi e profili di drogaggio personalizzati per R&S). I diametri dei wafer vanno da 2", 4", 6", 8" e 12" per adattarsi sia agli utensili tradizionali che alle fabbriche avanzate. Forniamo anche boules monocristalline e cristalli seed orientati con precisione per supportare la crescita dei cristalli in-house.

I nostri wafer 4H-N presentano densità di portatori da 1×10¹⁶ a 1×10¹⁹ cm⁻³ e resistività di 0,01–10 Ω·cm, offrendo un'eccellente mobilità elettronica e campi di breakdown superiori a 2 MV/cm, ideali per diodi Schottky, MOSFET e JFET. I substrati HPSI superano la resistività di 1×10¹² Ω·cm con densità di micropipe inferiori a 0,1 cm⁻², garantendo perdite minime per dispositivi RF e microonde. Il 3C-N cubico, disponibile nei formati da 2" e 4", consente l'eteroepitassia su silicio e supporta nuove applicazioni fotoniche e MEMS. I wafer 4H/6H-P di tipo P, drogati con alluminio a 1×10¹⁶–5×10¹⁸ cm⁻³, facilitano architetture di dispositivi complementari.

I wafer SiC PRIME vengono sottoposti a lucidatura chimico-meccanica fino a raggiungere una rugosità superficiale RMS <0,2 nm, una variazione di spessore totale inferiore a 3 µm e una curvatura <10 µm. I substrati DUMMY accelerano i test di assemblaggio e confezionamento, mentre i wafer RESEARCH presentano spessori epi-layer di 2-30 µm e un drogaggio personalizzato. Tutti i prodotti sono certificati mediante diffrazione a raggi X (curva di oscillazione <30 secondi d'arco) e spettroscopia Raman, con test elettrici (misurazioni Hall, profilazione C-V e scansione micropipe) che garantiscono la conformità JEDEC e SEMI.

Boules fino a 150 mm di diametro vengono coltivate tramite PVT e CVD con densità di dislocazione inferiori a 1×10³ cm⁻² e basso numero di micropipe. I cristalli di seme vengono tagliati entro 0,1° dall'asse C per garantire una crescita riproducibile e rese di taglio elevate.

Combinando più politipi, varianti di drogaggio, gradi di qualità, dimensioni dei wafer di SiC e produzione interna di boule e cristalli seed, la nostra piattaforma di substrati SiC semplifica le catene di fornitura e accelera lo sviluppo di dispositivi per veicoli elettrici, reti intelligenti e applicazioni in ambienti difficili.

Riassunto del wafer di SiC

Wafer di carburo di silicio (SiC)sono diventati il substrato SiC di scelta per l'elettronica ad alta potenza, alta frequenza e alta temperatura nei settori automobilistico, delle energie rinnovabili e aerospaziale. Il nostro portafoglio comprende i principali politipi e schemi di drogaggio: 4H drogato con azoto (4H-N), semi-isolante ad alta purezza (HPSI), 3C drogato con azoto (3C-N) e 4H/6H di tipo p (4H/6H-P), offerti in tre livelli di qualità: wafer di SiCPRIME (substrati completamente lucidati, di qualità per dispositivi), DUMMY (lappati o non lucidati per prove di processo) e RESEARCH (strati epi e profili di drogaggio personalizzati per R&S). I diametri dei wafer in SiC vanno da 2", 4", 6", 8" e 12" per adattarsi sia agli utensili tradizionali che alle fabbriche avanzate. Forniamo anche boule monocristalline e cristalli seed orientati con precisione per supportare la crescita dei cristalli internamente.

I nostri wafer SiC 4H-N presentano densità di portatori da 1×10¹⁶ a 1×10¹⁹ cm⁻³ e resistività di 0,01–10 Ω·cm, offrendo un'eccellente mobilità elettronica e campi di breakdown superiori a 2 MV/cm, ideali per diodi Schottky, MOSFET e JFET. I substrati HPSI superano la resistività di 1×10¹² Ω·cm con densità di micropipe inferiori a 0,1 cm⁻², garantendo perdite minime per dispositivi RF e microonde. Il 3C-N cubico, disponibile nei formati da 2" e 4", consente l'eteroepitassia su silicio e supporta nuove applicazioni fotoniche e MEMS. I wafer SiC di tipo P 4H/6H-P, drogati con alluminio a 1×10¹⁶–5×10¹⁸ cm⁻³, facilitano architetture di dispositivi complementari.

I wafer SiC PRIME vengono sottoposti a lucidatura chimico-meccanica fino a raggiungere una rugosità superficiale RMS <0,2 nm, una variazione di spessore totale inferiore a 3 µm e una curvatura <10 µm. I substrati DUMMY accelerano i test di assemblaggio e confezionamento, mentre i wafer RESEARCH presentano spessori epi-layer di 2–30 µm e un drogaggio personalizzato. Tutti i prodotti sono certificati mediante diffrazione a raggi X (curva di oscillazione <30 secondi d'arco) e spettroscopia Raman, con test elettrici (misurazioni Hall, profilazione C–V e scansione micropipe) che garantiscono la conformità JEDEC e SEMI.

Boules fino a 150 mm di diametro vengono coltivate tramite PVT e CVD con densità di dislocazione inferiori a 1×10³ cm⁻² e basso numero di micropipe. I cristalli di seme vengono tagliati entro 0,1° dall'asse C per garantire una crescita riproducibile e rese di taglio elevate.

Combinando più politipi, varianti di drogaggio, gradi di qualità, dimensioni dei wafer di SiC e produzione interna di boule e cristalli seed, la nostra piattaforma di substrati SiC semplifica le catene di fornitura e accelera lo sviluppo di dispositivi per veicoli elettrici, reti intelligenti e applicazioni in ambienti difficili.

Scheda tecnica del wafer SiC tipo 4H-N da 6 pollici

| Scheda tecnica dei wafer SiC da 6 pollici | ||||

| Parametro | Sottoparametro | Grado Z | Grado P | Grado D |

| Diametro | 149,5–150,0 millimetri | 149,5–150,0 millimetri | 149,5–150,0 millimetri | |

| Spessore | 4H‑N | 350 µm ± 15 µm | 350 µm ± 25 µm | 350 µm ± 25 µm |

| Spessore | 4H‑SI | 500 µm ± 15 µm | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Orientamento del wafer | Fuori asse: 4,0° verso <11-20> ±0,5° (4H-N); Sull'asse: <0001> ±0,5° (4H-SI) | Fuori asse: 4,0° verso <11-20> ±0,5° (4H-N); Sull'asse: <0001> ±0,5° (4H-SI) | Fuori asse: 4,0° verso <11-20> ±0,5° (4H-N); Sull'asse: <0001> ±0,5° (4H-SI) | |

| Densità del microtubo | 4H‑N | ≤ 0,2 cm⁻² | ≤ 2 cm⁻² | ≤ 15 cm⁻² |

| Densità del microtubo | 4H‑SI | ≤ 1 cm⁻² | ≤ 5 cm⁻² | ≤ 15 cm⁻² |

| Resistività | 4H‑N | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | 0,015–0,028 Ω·cm |

| Resistività | 4H‑SI | ≥ 1×10¹⁰ Ω·cm | ≥ 1×10⁵ Ω·cm | |

| Orientamento primario piatto | [10-10] ± 5,0° | [10-10] ± 5,0° | [10-10] ± 5,0° | |

| Lunghezza piana primaria | 4H‑N | 47,5 millimetri ± 2,0 millimetri | ||

| Lunghezza piana primaria | 4H‑SI | Tacca | ||

| Esclusione del bordo | 3 millimetri | |||

| Warp/LTV/TTV/Arco | ≤2,5 µm / ≤6 µm / ≤25 µm / ≤35 µm | ≤5 µm / ≤15 µm / ≤40 µm / ≤60 µm | ||

| Rugosità | Polacco | Ra ≤ 1 nm | ||

| Rugosità | CMP | Ra ≤ 0,2 nm | Ra ≤ 0,5 nm | |

| crepe sui bordi | Nessuno | Lunghezza cumulativa ≤ 20 mm, singola ≤ 2 mm | ||

| Piastre esagonali | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 0,1% | Area cumulativa ≤ 1% | |

| Aree politipiche | Nessuno | Area cumulativa ≤ 3% | Area cumulativa ≤ 3% | |

| Inclusioni di carbonio | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 3% | ||

| Graffi superficiali | Nessuno | Lunghezza cumulativa ≤ 1 × diametro del wafer | ||

| Chip di bordo | Nessuno consentito ≥ 0,2 mm di larghezza e profondità | Fino a 7 chip, ≤ 1 mm ciascuno | ||

| TSD (dislocazione della vite filettata) | ≤ 500 cm⁻² | N / A | ||

| BPD (lussazione del piano base) | ≤ 1000 cm⁻² | N / A | ||

| Contaminazione superficiale | Nessuno | |||

| Confezione | Cassetta multi-wafer o contenitore per wafer singolo | Cassetta multi-wafer o contenitore per wafer singolo | Cassetta multi-wafer o contenitore per wafer singolo | |

Scheda tecnica del wafer SiC tipo 4H-N da 4 pollici

| Scheda tecnica del wafer SiC da 4 pollici | |||

| Parametro | Produzione MPD pari a zero | Grado di produzione standard (grado P) | Grado fittizio (grado D) |

| Diametro | 99,5 mm–100,0 mm | ||

| Spessore (4H-N) | 350 µm±15 µm | 350 µm±25 µm | |

| Spessore (4H-Si) | 500 µm±15 µm | 500 µm±25 µm | |

| Orientamento del wafer | Fuori asse: 4,0° verso <1120> ±0,5° per 4H-N; Sull'asse: <0001> ±0,5° per 4H-Si | ||

| Densità del microtubo (4H-N) | ≤0,2 cm⁻² | ≤2 cm⁻² | ≤15 cm⁻² |

| Densità del microtubo (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Resistività (4H-N) | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | |

| Resistività (4H-Si) | ≥1E10 Ω·cm | ≥1E5 Ω·cm | |

| Orientamento primario piatto | [10-10] ±5,0° | ||

| Lunghezza piana primaria | 32,5 millimetri ±2,0 millimetri | ||

| Lunghezza piatta secondaria | 18,0 millimetri ±2,0 millimetri | ||

| Orientamento secondario piatto | Faccia in silicone rivolta verso l'alto: 90° CW dalla superficie piana principale ±5,0° | ||

| Esclusione del bordo | 3 millimetri | ||

| LTV/TTV/Bow Warp | ≤2,5 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Rugosità | Ra polacco ≤1 nm; CMP Ra ≤0,2 nm | Ra ≤0,5 nm | |

| Crepe sui bordi causate da luce ad alta intensità | Nessuno | Nessuno | Lunghezza cumulativa ≤10 mm; lunghezza singola ≤2 mm |

| Piastre esagonali ad alta intensità luminosa | Area cumulativa ≤0,05% | Area cumulativa ≤0,05% | Area cumulativa ≤0,1% |

| Aree politipiche mediante luce ad alta intensità | Nessuno | Area cumulativa ≤3% | |

| Inclusioni visive di carbonio | Area cumulativa ≤0,05% | Area cumulativa ≤3% | |

| Graffi sulla superficie del silicio causati dalla luce ad alta intensità | Nessuno | Lunghezza cumulativa ≤1 diametro del wafer | |

| Chip di bordo tramite luce ad alta intensità | Nessuno consentito ≥0,2 mm di larghezza e profondità | 5 consentiti, ≤1 mm ciascuno | |

| Contaminazione della superficie del silicio da parte della luce ad alta intensità | Nessuno | ||

| Dislocazione della vite filettata | ≤500 cm⁻² | N / A | |

| Confezione | Cassetta multi-wafer o contenitore per wafer singolo | Cassetta multi-wafer o contenitore per wafer singolo | Cassetta multi-wafer o contenitore per wafer singolo |

Scheda tecnica del wafer SiC tipo HPSI da 4 pollici

| Scheda tecnica del wafer SiC tipo HPSI da 4 pollici | |||

| Parametro | Grado di produzione Zero MPD (grado Z) | Grado di produzione standard (grado P) | Grado fittizio (grado D) |

| Diametro | 99,5–100,0 millimetri | ||

| Spessore (4H-Si) | 500 µm ±20 µm | 500 µm ±25 µm | |

| Orientamento del wafer | Fuori asse: 4,0° verso <11-20> ±0,5° per 4H-N; Sull'asse: <0001> ±0,5° per 4H-Si | ||

| Densità del microtubo (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Resistività (4H-Si) | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |

| Orientamento primario piatto | (10-10) ±5,0° | ||

| Lunghezza piana primaria | 32,5 millimetri ±2,0 millimetri | ||

| Lunghezza piatta secondaria | 18,0 millimetri ±2,0 millimetri | ||

| Orientamento secondario piatto | Faccia in silicone rivolta verso l'alto: 90° CW dalla superficie piana principale ±5,0° | ||

| Esclusione del bordo | 3 millimetri | ||

| LTV/TTV/Bow Warp | ≤3 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Rugosità (faccia C) | Polacco | Ra ≤1 nm | |

| Rugosità (faccia Si) | CMP | Ra ≤0,2 nm | Ra ≤0,5 nm |

| Crepe sui bordi causate da luce ad alta intensità | Nessuno | Lunghezza cumulativa ≤10 mm; lunghezza singola ≤2 mm | |

| Piastre esagonali ad alta intensità luminosa | Area cumulativa ≤0,05% | Area cumulativa ≤0,05% | Area cumulativa ≤0,1% |

| Aree politipiche mediante luce ad alta intensità | Nessuno | Area cumulativa ≤3% | |

| Inclusioni visive di carbonio | Area cumulativa ≤0,05% | Area cumulativa ≤3% | |

| Graffi sulla superficie del silicio causati dalla luce ad alta intensità | Nessuno | Lunghezza cumulativa ≤1 diametro del wafer | |

| Chip di bordo tramite luce ad alta intensità | Nessuno consentito ≥0,2 mm di larghezza e profondità | 5 consentiti, ≤1 mm ciascuno | |

| Contaminazione della superficie del silicio da parte della luce ad alta intensità | Nessuno | Nessuno | |

| Lussazione della vite filettata | ≤500 cm⁻² | N / A | |

| Confezione | Cassetta multi-wafer o contenitore per wafer singolo | ||

Applicazione del wafer SiC

-

Moduli di potenza in wafer SiC per inverter EV

I MOSFET e i diodi basati su wafer di SiC, realizzati su substrati di wafer di SiC di alta qualità, offrono perdite di commutazione estremamente basse. Sfruttando la tecnologia dei wafer di SiC, questi moduli di potenza funzionano a tensioni e temperature più elevate, consentendo inverter di trazione più efficienti. L'integrazione dei die di wafer di SiC negli stadi di potenza riduce i requisiti di raffreddamento e l'ingombro, dimostrando il pieno potenziale dell'innovazione dei wafer di SiC. -

Dispositivi RF e 5G ad alta frequenza su wafer SiC

Gli amplificatori RF e gli interruttori realizzati su piattaforme di wafer SiC semi-isolanti presentano conduttività termica e tensione di rottura superiori. Il substrato del wafer SiC riduce al minimo le perdite dielettriche alle frequenze GHz, mentre la resistenza del materiale del wafer SiC consente un funzionamento stabile in condizioni di alta potenza e alta temperatura, rendendo il wafer SiC il substrato di scelta per le stazioni base 5G e i sistemi radar di nuova generazione. -

Substrati optoelettronici e LED da wafer SiC

I LED blu e UV sviluppati su substrati di wafer SiC beneficiano di un eccellente adattamento del reticolo e di una buona dissipazione del calore. L'utilizzo di un wafer SiC con superficie C lucida garantisce strati epitassiali uniformi, mentre la durezza intrinseca del wafer SiC consente un sottile assottigliamento del wafer e un packaging affidabile del dispositivo. Questo rende il wafer SiC la piattaforma ideale per applicazioni LED ad alta potenza e lunga durata.

Domande e risposte sui wafer SiC

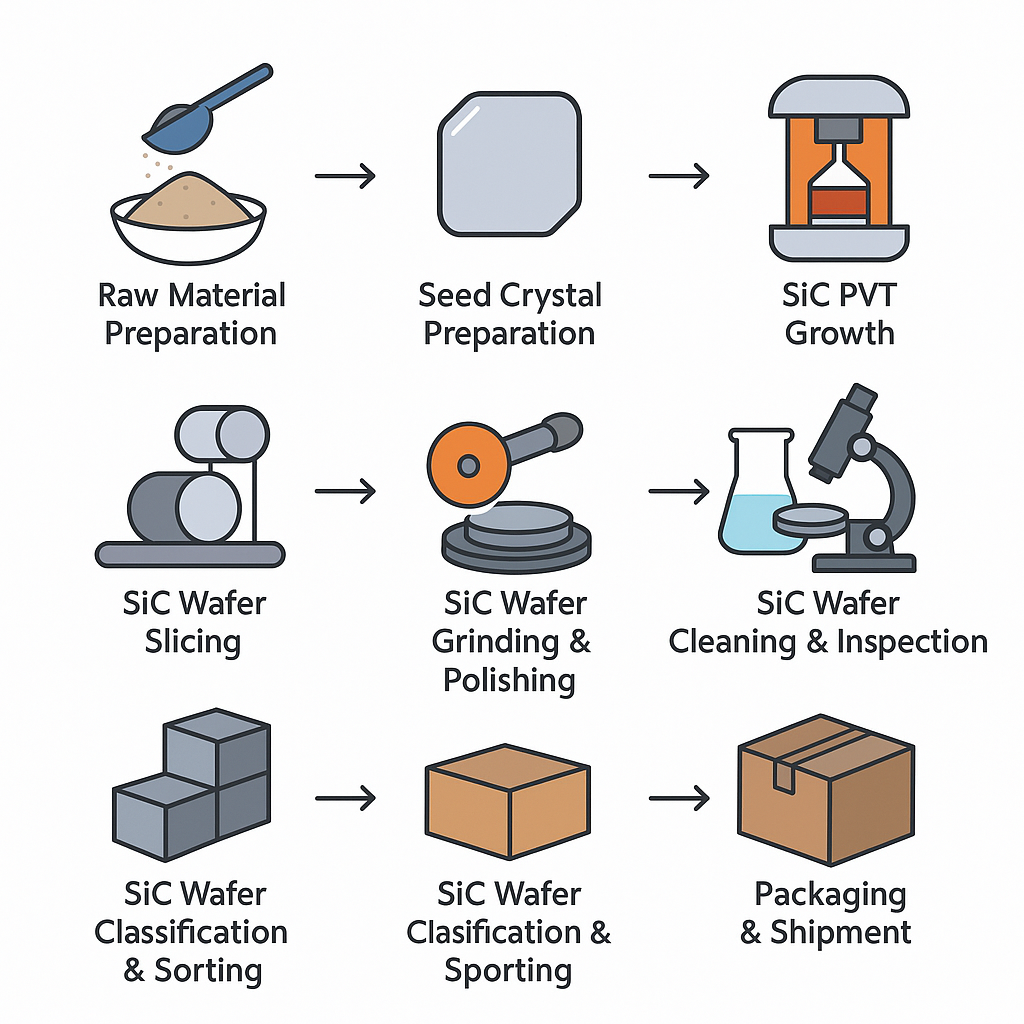

1. D: Come vengono prodotti i wafer di SiC?

UN:

Wafer di SiC prodottiPassaggi dettagliati

-

wafer di SiCPreparazione delle materie prime

- Utilizzare polvere di SiC di grado ≥5N (impurità ≤1 ppm).

- Setacciare e precuocere per rimuovere i residui di carbonio o composti di azoto.

-

SiCPreparazione dei cristalli di seme

-

Prendi un pezzo di monocristallo 4H-SiC e taglialo lungo l'orientamento 〈0001〉 fino a ottenere ~10 × 10 mm².

-

Lucidatura di precisione a Ra ≤0,1 nm e marcatura dell'orientamento dei cristalli.

-

-

SiCCrescita PVT (trasporto fisico del vapore)

-

Caricare il crogiolo di grafite: fondo con polvere di SiC, parte superiore con cristalli di innesco.

-

Evacuare a 10⁻³–10⁻⁵ Torr o riempire con elio ad alta purezza a 1 atm.

-

Riscaldare la zona della fonte a 2100–2300 ℃, mantenere la zona dei semi a 100–150 ℃ più fresca.

-

Controllare la velocità di crescita a 1–5 mm/h per bilanciare qualità e produttività.

-

-

SiCRicottura del lingotto

-

Ricottura del lingotto di SiC così come è cresciuto a 1600–1800 ℃ per 4–8 ore.

-

Scopo: alleviare le sollecitazioni termiche e ridurre la densità delle dislocazioni.

-

-

SiCTaglio delle cialde

-

Utilizzare una sega a filo diamantato per tagliare il lingotto in fette spesse 0,5–1 mm.

-

Ridurre al minimo le vibrazioni e le forze laterali per evitare micro-crepe.

-

-

SiCWaferMolatura e lucidatura

-

Macinazione grossolanaper rimuovere i danni da taglio (rugosità ~10–30 µm).

-

macinazione fineper ottenere una planarità ≤5 µm.

-

Lucidatura chimico-meccanica (CMP)per raggiungere una finitura a specchio (Ra ≤0,2 nm).

-

-

SiCWaferPulizia e ispezione

-

Pulizia ad ultrasuoniin soluzione Piranha (H₂SO₄:H₂O₂), acqua deionizzata, quindi IPA.

-

Spettroscopia XRD/Ramanper confermare il politipo (4H, 6H, 3C).

-

Interferometriaper misurare la planarità (<5 µm) e la deformazione (<20 µm).

-

Sonda a quattro puntiper testare la resistività (ad esempio HPSI ≥10⁹ Ω·cm).

-

Ispezione dei difettial microscopio a luce polarizzata e al tester per graffi.

-

-

SiCWaferClassificazione e ordinamento

-

Ordina i wafer in base al politipo e al tipo elettrico:

-

4H-SiC tipo N (4H-N): concentrazione del portatore 10¹⁶–10¹⁸ cm⁻³

-

4H-SiC semi-isolante ad alta purezza (4H-HPSI): resistività ≥10⁹ Ω·cm

-

6H-SiC tipo N (6H-N)

-

Altri: 3C-SiC, tipo P, ecc.

-

-

-

SiCWaferImballaggio e spedizione

2. D: Quali sono i principali vantaggi dei wafer SiC rispetto ai wafer di silicio?

A: Rispetto ai wafer di silicio, i wafer SiC consentono:

-

Funzionamento ad alta tensione(>1.200 V) con resistenza di conduzione inferiore.

-

Maggiore stabilità della temperatura(>300 °C) e una migliore gestione termica.

-

Velocità di commutazione più elevatecon minori perdite di commutazione, riducendo il raffreddamento a livello di sistema e le dimensioni dei convertitori di potenza.

4. D: Quali difetti comuni influiscono sulla resa e sulle prestazioni dei wafer SiC?

R: I difetti principali nei wafer di SiC includono micropipe, dislocazioni del piano basale (BPD) e graffi superficiali. I micropipe possono causare guasti catastrofici del dispositivo; le BPD aumentano la resistenza di on nel tempo; e i graffi superficiali portano alla rottura del wafer o a una scarsa crescita epitassiale. Un'ispezione rigorosa e la mitigazione dei difetti sono quindi essenziali per massimizzare la resa dei wafer di SiC.

Data di pubblicazione: 30-06-2025